**appunti**

www.centroappunti.it

Corso Luigi Einaudi, 55/B - Torino

Appunti universitari

Tesi di laurea

Cartoleria e cancelleria

Stampa file e fotocopie

Print on demand

Rilegature

NUMERO: 1675A -

ANNO: 2015

# APPUNTI

STUDENTE: Fissore

MATERIA: Sistemi Elettronici a Basso Consumo LowPower,

Prof.Zamboni

Il presente lavoro nasce dall'impegno dell'autore ed è distribuito in accordo con il Centro Appunti. Tutti i diritti sono riservati. È vietata qualsiasi riproduzione, copia totale o parziale, dei contenuti inseriti nel presente volume, ivi inclusa la memorizzazione, rielaborazione, diffusione o distribuzione dei contenuti stessi mediante qualunque supporto magnetico o cartaceo, piattaforma tecnologica o rete telematica, senza previa autorizzazione scritta dell'autore.

ATTENZIONE: QUESTI APPUNTI SONO FATTI DA STUDENTI E NON SONO STATI VISIONATI DAL DOCENTE.

IL NOME DEL PROFESSORE, SERVE SOLO PER IDENTIFICARE IL CORSO.

## Low-Power Electronics System

Prof. Maurizio Zamboni

maurizio.zamboni@polito.it

phone number +39 11 090 4079

Electronics Department

Politecnico di Torino

Appunti di Giorgio Fissore

Disponibili in centro stampa

SEBC-L1

MZ 1

## Low-Power Electronics System

### Timetable

|                  | lunedì 09/03/2015                                                             | martedì 10/03/2015                                                            | mercoledì 11/03/2015 | giovedì 12/03/2015 | venerdì 13/03/2015 |

|------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------------|--------------------|--------------------|

| 8 <sup>00</sup>  |                                                                               |                                                                               |                      |                    |                    |

| 9 <sup>00</sup>  |                                                                               |                                                                               |                      |                    |                    |

| 10 <sup>00</sup> |                                                                               |                                                                               |                      |                    |                    |

| 11 <sup>00</sup> |                                                                               |                                                                               |                      |                    |                    |

| 12 <sup>00</sup> | Sistemi elettronici a<br>basso...<br>ZAMBONI MAURIZIO<br>AA - ZZ - 0<br>LED 3 | Sistemi elettronici a<br>basso...<br>ZAMBONI MAURIZIO<br>AA - ZZ - 0<br>LED 3 |                      |                    |                    |

| 13 <sup>00</sup> |                                                                               |                                                                               |                      |                    |                    |

| 14 <sup>00</sup> |                                                                               |                                                                               |                      |                    |                    |

| 15 <sup>00</sup> |                                                                               |                                                                               |                      |                    |                    |

| 16 <sup>00</sup> |                                                                               |                                                                               |                      |                    |                    |

SEBC-L1

MZ 2

7 volte in lab:

10 marzo

17 marzo

14 aprile

28 aprile

12 maggio

26 maggio

9 giugno?

## Low-Power System Design

### FINAL EXAM

Discussion on course topics

Lab sessions (1/3 of final grade)

Optional Final Project instead of

Lab Reports (2/3 of final grade +

bonus) (suggested only if really motivated)

to reach 30LODE/30

Esame solo orale,

con possibilità di

sostenerlo

praticamente tutte

le settimane

concordato con il

docente

Le relazioni di

laboratorio

possono essere

consegnate anche

dopo aver dato gli

esami.

Mod by Giorgio Fissore, pag 1

L1-Introduction.key - 22 Feb 2015

## Low-Power System Design

### COURSE MATERIAL:

Low-Power Design Essentials - J. Rabaey - Springer, 2009

Low-power CMOS VLSI Circuit Design – K. Roy, S. C. Prasad J. WILEY & SONS

Workbook as a collection of slides coming from different sources (available also on "Portale della didattica")

Slides partially adapted from Low-Power Design Essentials, Springer 2009. © J. Rabaey.

Series of papers also available on "Portale della didattica"

Il libro che potrebbe essere più interessante.

Ci sono in più appunti presi qualche anno fa

SEBC-L1

MZ 7

SEBC-L1

MZ 8

## Lecture 1 Introduction to Low-Power Design

- Motivation

- Historical Drivers of Low-Power Design

- Microprocessor Scaling

- Power Sources

- Low-Power Design Methods

SEBC-L1

MZ 9

Mod by Giorgio Fissore, pag 3

L1-Introduction.key - 22 Feb 2015

## Motivation for Low-Power Design

International Technology Roadmap for Semiconductors

| Year of Introduction              | 1999    | 2000    | 2001    | 2004    | 2008    | 2011    | 2014    |

|-----------------------------------|---------|---------|---------|---------|---------|---------|---------|

| Technology node [nm]              | 180     |         | 130     | 90      | 60      | 40      | 30      |

| Supply [V]                        | 1.5-1.8 | 1.5-1.8 | 1.2-1.5 | 0.9-1.2 | 0.6-0.9 | 0.5-0.6 | 0.3-0.6 |

| Wiring levels                     | 6-7     | 6-7     | 7       | 8       | 9       | 9-10    | 10      |

| Max frequency [GHz], Local-Global | 1.2     | 1.6-1.4 | 2.1-1.6 | 3.5-2   | 7.1-2.5 | 11-3    | 14.9    |

| Max $\mu$ P power [W]             | 90      | 106     | 130     | 160     | 171     | 177     | 186     |

| Bat. power [W]                    | 1.4     | 1.7     | 2.0     | 2.4     | 2.1     | 2.3     | 2.5     |

Node years: 2007/65nm, 2010/45nm, 2013/33nm, 2016/23nm

SEBC-L1

MZ 13

## Historical Drivers of Low-Power Design

- Pocket calculators

- Hearing aids

- Implantable pacemakers and cardiac defibrillators

- Portable military equipment for individual soldiers

- Wristwatches

- Wireless computing ..... BUT NOT ONLY!!!!

SEBC-L1

MZ 14

## Historical Drivers of Low-Power Design

- 20% of electrical energy in Amsterdam due to telecom!!!

- In US 9% of energy consumption due to Internet!!!

- 2 Mbytes transfer through the net consumes the energy of 1 pound of coal 1 libra di carbonio

SEBC-L1

MZ 15

Mod by Giorgio Fissore, pag 5

L1-Introduction.key - 22 Feb 2015

## Power the Dominant Design Constraint

SEBC-L1

[Ref: R. Schmidt, ACEED'03]

MZ 19

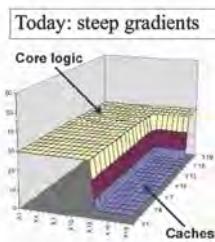

## Chip Architecture and Power Density

Integration of diverse functionality on SoC causes major variations in activity (and hence power density)

The past: temperature uniformity

Temperature variations cause performance degradation – higher temperature means slower clock speed

La tecnologia costruita "più in 3D" genera gradienti di temperatura all'interno del dispositivo.

(si sceglie la distribuzione dei vari componenti all'interno del chip, anche in base a questi gradienti - es no due parti vicine a 30° e 100° per non ridurre la vita dello stesso)

SEBC-L1

[Ref: R. Yung, ESSCIRC'02]

MZ 20

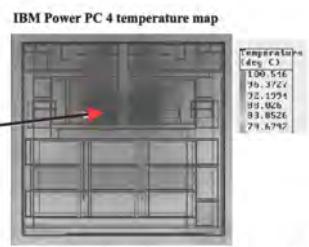

## Temperature Gradients (and Performance)

Hot spot:

138 W/cm<sup>2</sup>

(3.6 x chip avg flux)

SEBC-L1

[Ref: R. Schmidt, ACEED'03]

MZ 21

Mod by Giorgio Fissore, pag 7

L1-Introduction.key - 22 Feb 2015

### Battery Storage a Limiting Factor

- Basic technology has evolved little

- store energy using a chemical reaction

- Battery capacity increases between 3% and 7 % per year (doubled during the 90's, relatively flat before that)

- Energy density/size, safe handling are limiting factor

| Energy density of material | kWh/kg |

|----------------------------|--------|

| Gasoline                   | 14     |

| Lead-Acid                  | 0.04   |

| Li polymer                 | 0.15   |

For extensive information on energy density of various materials, check [http://en.wikipedia.org/wiki/Energy\\_density](http://en.wikipedia.org/wiki/Energy_density)

SEBC-L1

MZ 25

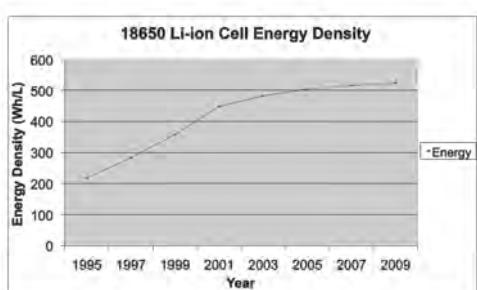

### Battery Evolution

Accelerated since the 1990's, but slower than IC power growth.

SEBC-L1

MZ 26

### Battery Technology Saturating

Battery capacity naturally plateaus as systems develop

SEBC-L1

[Courtesy: M. Doyle, Dupont]

MZ 27

Mod by Giorgio Fissore, pag 9

L1-Introduction.key - 22 Feb 2015

### How much Energy Storage in 1 cm<sup>3</sup>?

|                   | J/cm <sup>3</sup> | μW/cm <sup>3</sup> /year |

|-------------------|-------------------|--------------------------|

| Micro Fuel cell   | 3500              | 110                      |

| Primary battery   | 2880              | 90                       |

| Secondary battery | 1080              | 34                       |

| Ultracapacitor    | 100               | 3.2                      |

Micro fuel cell

SEBC-L1

MZ 31

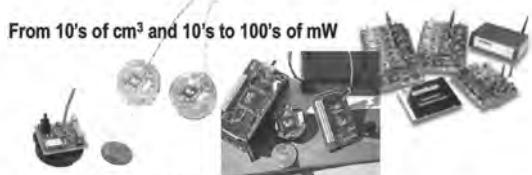

### Power the Dominant Design Constraint (3)

Exciting emerging applications require "zero-power"

Example: Computation/Communication Nodes for Wireless Sensor Networks

**Meso-scale low-cost wireless transceivers for ubiquitous wireless data acquisition that**

- \* are fully integrated

- Size smaller than 1 cm<sup>3</sup>

- \* are cheap

- At or below 1\$

- \* minimize power/energy dissipation

- Limiting power dissipation to 100 μW enables energy scavenging

- + and form self-configuring, robust, ad-hoc networks containing 100's to 1000's of nodes

SEBC-L1

[Ref: J. Rabney, ISSCC'01]

MZ 32

Applicazioni a "zero power", applicazioni a consumo praticamente nullo che potrebbero non richiedere una batteria.

Ciò vuol dire trovare il modo di alimentare questi sistemi direttamente dall'ambiente.

Vedi slide 35 per esempi

### How to Make Electronics Truly Disappear?

To 10's of mm<sup>3</sup> and 10's of μW

SEBC-L1

MZ 33

Mod by Giorgio Fissore, pag 11

L1-Introduction.key - 22 Feb 2015

## Power versus Energy

- **Power** in high performance systems

- Heat removal

- Peak power - power delivery

- **Energy** in portable systems

- Battery life

- Energy/power in “zero-power systems”

- Energy-scavenging and storage capabilities

- Dynamic (energy) vs. static (power) consumption

- Determined by operation modes

I parametri di potenza ed energia sono importanti per motivi diversi:

La potenza è legata principalmente alla capacità di portare via calore dal mio dispositivo.

La potenza di picco è invece legata al fatto che questa causa un'alta corrente di picco, che, se il filo ha una resistenza anche piccola, genera alte tensioni che possono disturbare; in più, se non abbastanza spesso, il filo rischia di rompersi.

L'energia ci interessa invece in termini di tempo di vita della batteria.

SEBC-L1

MZ 37

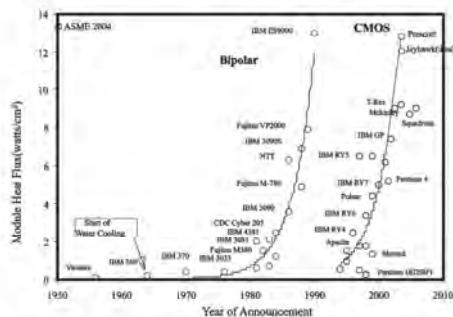

## Power Evolution over Technology Generations

Introduction of CMOS over bipolar bought industry 10 years

(example: IBM mainframe processors)

SEBC-L1

[Ref: R. Chu, JEP'04]

MZ 38

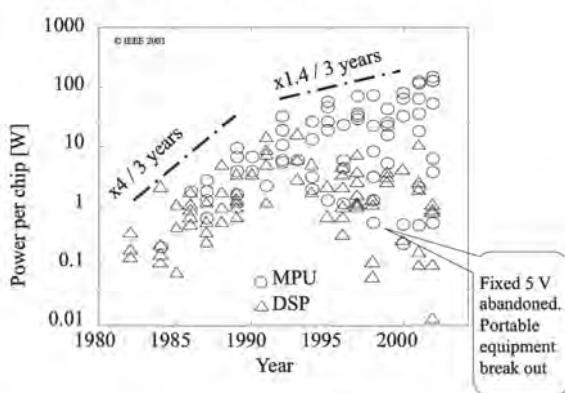

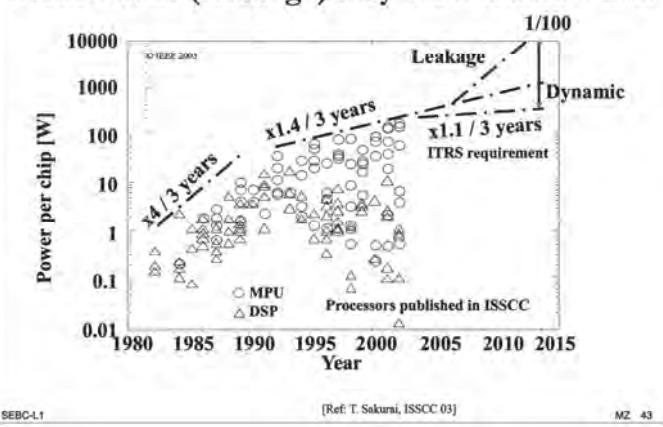

## Power Trends for Processors

SEBC-L1

[Ref: T. Sakurai, ISSCC'03]

MZ 39

Mod by Giorgio Fissore, pag 13

L1-Introduction.key - 22 Feb 2015

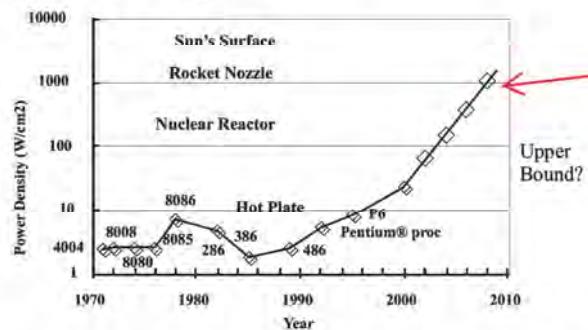

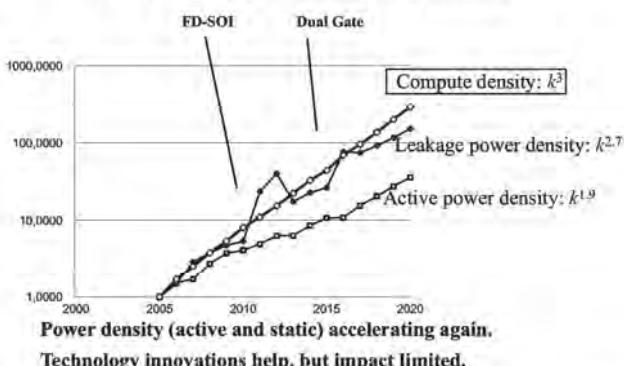

## Static Power (Leakage) may Ruin Moore's Law

## Power Density Increases

Unsustainable in the long term

Se non avessimo ridotto i consumi, un processore utilizzerebbe la potenza di un razzo in accensione

## Projecting Into the Future

Mod by Giorgio Fissore, pag 15

L1-Introduction.key - 22 Feb 2015

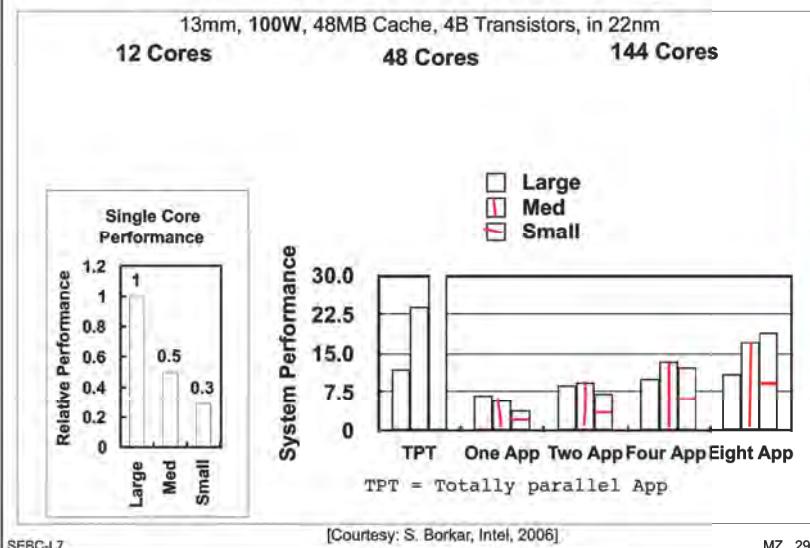

## A 20 nm Scenario

### Assume $V_{DD} = 1.2V$

- delay < 5 ps

- Assuming no architectural changes, digital circuits could be run at 30 GHz FO4

- Leading to power density of 20 kW/cm<sup>2</sup> (??)

### Reduce $V_{DD}$ to 0.6V

- FO4 delay = 10 ps

- The clock frequency is lowered to 10 GHz

- Power density reduces to 5 kW/cm<sup>2</sup> (still way too high)

SEBC-L1

[Ref: S. Borkar, Intel]

MZ 49

## A 20 nm Scenario (cntd)

Assume optimistically that we can design FETs (Dual-Gate, FinFet, or whatever) that operate at 1 kW/cm<sup>2</sup> for FO4 = 10 ps and  $V_{DD} = 0.6$  V [Frank, Proc. IEEE, 3/01]

- For a 2cm x 2cm high-performance microprocessor die, this means 4kW power dissipation.

- If die power has to be limited to 200W, only 5% of these devices can switching at any time, assuming that nothing else dissipates power.

SEBC-L1

[Ref: S. Borkar, Intel]

MZ 50

## An Era of Power-Limited Technology Scaling

### • Technology innovations offer some relief

Devices that perform better at low voltage without leaking too much

### • But also are adding major grieve

Impact of increasing process variations and various failure mechanisms more pronounced in low-power design regime.

### • Most plausible scenario

Circuit and system level solutions essential to keep power/energy dissipation in check

Slow down growth in computational density, and use obtained slack to control power density increase.

Introduce design techniques to operate circuit at nominal, not worst-case, conditions

SEBC-L1

MZ 51

Mod by Giorgio Fissore, pag 17

L1-Introduction.key - 22 Feb 2015

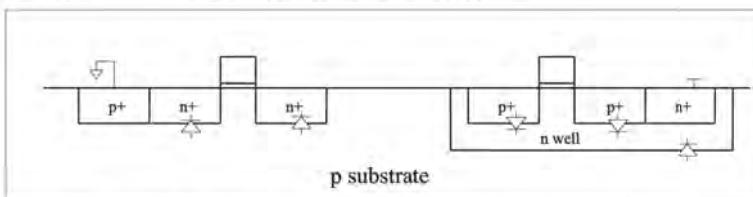

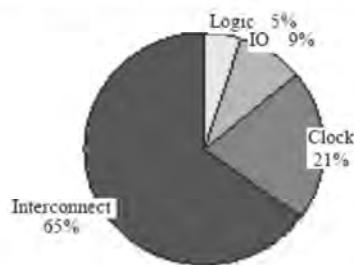

## Where is Power Dissipated in CMOS?

- Active (Dynamic) power

- (Dis)charging capacitors

- Short-circuit power

- Both pull-up and pull-down on during transition

- Static (leakage) power

- Transistors are imperfect switches

- Static currents

- Biasing currents

Quando il circuito

necessita di una

CC continua.

Contributo che si

cerca di evitare, ma

non sempre si

riesce.

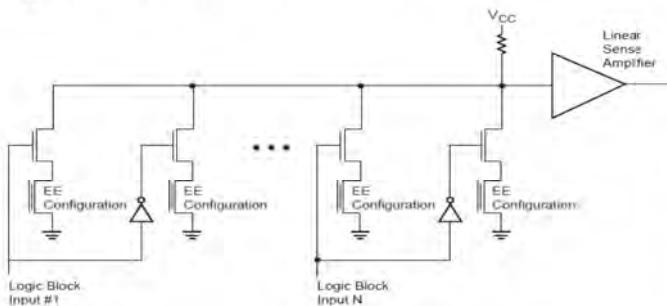

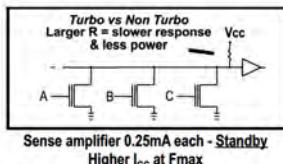

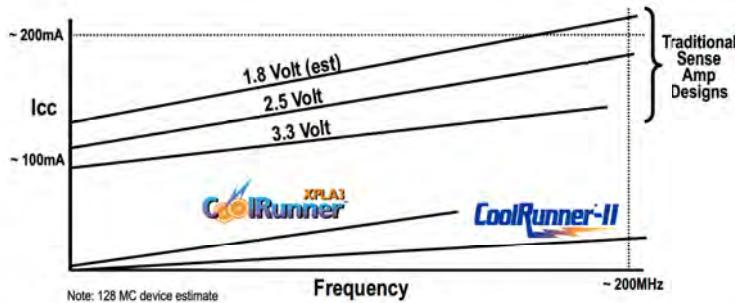

Esempio: sense amplifier usati nelle flash, hanno bisogno di essere alimentati in continua

SEBC-L2

## Active (or Dynamic) Power

Key property of active power:

$$P_{dyn} \propto f$$

with  $f$  the switching frequency

### Sources:

- Charging and discharging capacitors

- Temporary glitches (dynamic hazards)

- Short-circuit currents

SEBC-L2

MZ 5

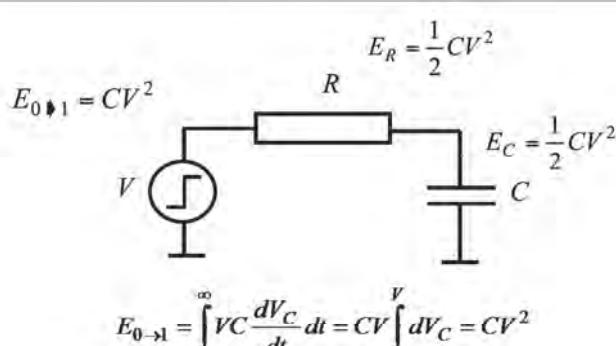

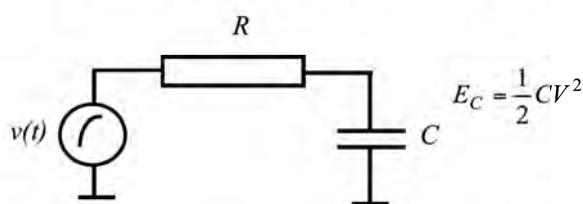

## Charging Capacitors

### Applying a voltage step

Value of  $R$  does not impact energy!

Mod by Giorgio Fissore, pag 19

SEBC-12

MZ 6

## Charging Capacitors

Using constant voltage or current driver?

$$\begin{aligned} E_{\text{constant\_current}} &< E_{\text{constant\_voltage}} \\ \text{if} \\ T &> 2RC \end{aligned}$$

Energy dissipated using constant current charging can be made arbitrarily small at the expense of delay:

**Adiabatic charging**

Note:  $t_p(RC) = 0.69 RC$

$t_{0 \rightarrow 90\%}(RC) = 2.3 RC$

## Charging Capacitors

Driving using a sine wave (e.g. from resonant circuit)

Energy dissipated in resistor can be made arbitrarily small if frequency  $\omega \ll 1/RC$

(output signal in phase with input sinusoid)

## Dynamic Power Consumption

Power = Energy/transition • Transition rate

$$\begin{aligned} &= C_L V_{DD}^2 \cdot f_{0 \rightarrow 1} \\ &= C_L V_{DD}^2 \cdot f \cdot P_{0 \rightarrow 1} \\ &= C_{\text{switched}} V_{DD}^2 \cdot f \end{aligned}$$

- Power dissipation is data dependent – depends on the switching probability

- Switched capacitance  $C_{\text{switched}} = P_{0 \rightarrow 1} C_L = E_{\text{sw}} C_L$  ( $E_{\text{sw}}$  is called the switching activity)

Questo transition rate può essere espresso come prodotto tra (sistemi sincroni):

la frequenza ed il numero di volte che il nostro disp cambia stato (switching activity)

Switching activity = (cambi di stato del disp)/(colpi di CLK)

FORMULA DA RICORDARE:

$$P = C_L \cdot V_{DD}^2 \cdot f \cdot E_{\text{sw}}$$

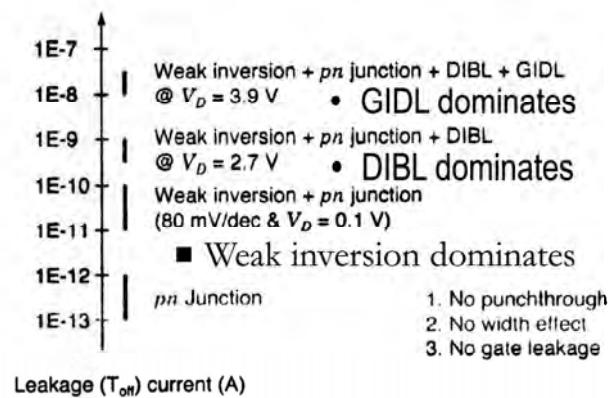

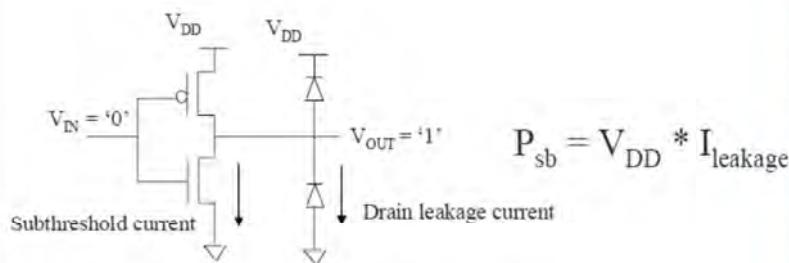

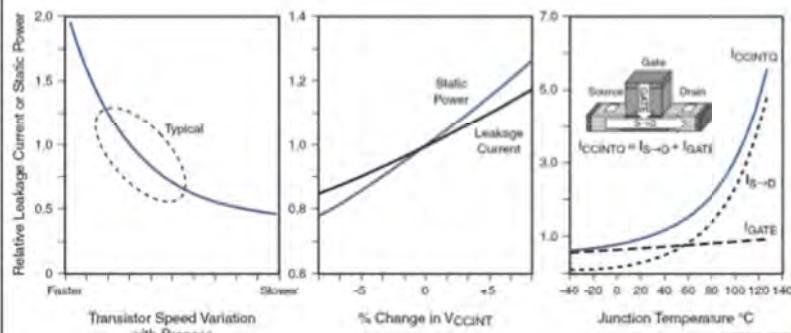

# Transistors Leak

- Drain leakage

- Diffusion currents

- Drain-induced barrier lowering (DIBL)

- Junction leakages

- Gate-induced drain leakage (GIDL)

- Gate leakage

- Tunneling currents through thin oxide

Transistori piccoli > cattivi interruttori, poiché differenze tra interdizione e zona attiva troppo piccole fanno sì che il transistor non si spenga mai del tutto.

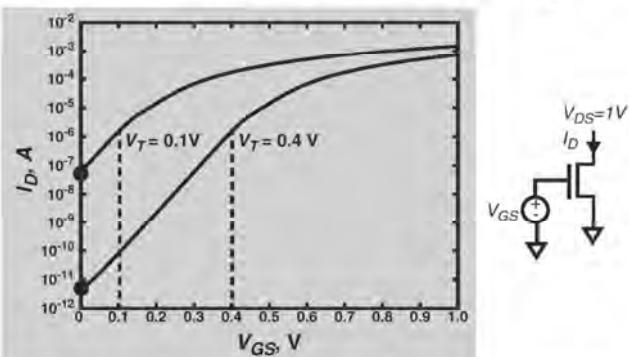

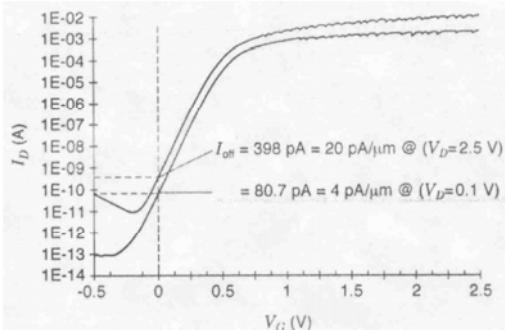

## Sub-threshold Leakage

Off-current increases exponentially when reducing  $V_{TH}$

$$I_{leak} = I_0 \frac{W}{W_0} 10^{\frac{-V_{TH}}{S}} \quad \Rightarrow \quad P_{leak} = V_{DD} \cdot I_{leak}$$

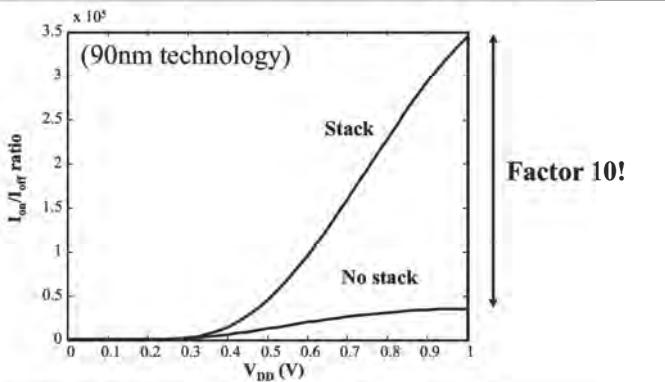

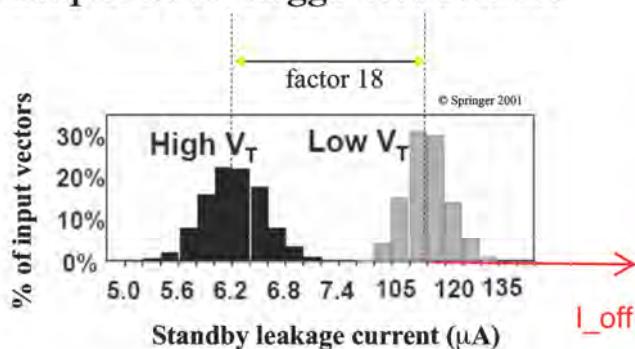

Se, per qualsiasi motivo, il dispositivo riduce la sua tensione di soglia, la sua transcaratteristica (I/V) si sposta a sinistra (vedi immagine). E ciò porta ad aumentare la corrente di parecchio (quattro ordini di grandezza); il legame tra la off-current (corrente a transistor spento) e la  $V_T$  è infatti esponenziale!!

Off-current aumenta exp con  $V_t$

## Sub-Threshold Leakage

Leakage current increases with drain voltage (mostly due to DIBL)

$$I_{leak} = I_0 \frac{W}{W_0} 10^{\frac{-V_{TH} + \lambda_d V_{DS}}{S}} \quad (\text{for } V_{DS} > 3 kT/q)$$

Hence

$$P_{leak} = (I_0 \frac{W}{W_0} 10^{\frac{-V_{TH}}{S}}) (V_{DD} 10^{\frac{\lambda_d V_{DS}}{S}})$$

Leakage Power strong function of supply voltage

Si può inoltre dimostrare che la  $I_{leak}$  aumenta sempre exp con la  $V_{DS}$ .

Dobbiamo quindi cercare di avere trans con la minima  $V_{DS}$  possibile

Mod by Giorgio Fiss

Mettendo due trans in serie (apparentemente assurdo) dimezzo la  $V_{DS}$  su di loro, e quindi abbasso  $I_{leak}$  non di un mezzo, ma di un esponenziale a base 10

## Other sources of static power dissipation

- Diode (drain-substrate) reverse bias currents

Il consumo statico vero e proprio è invece dovuto alla presenza di elementi, come il sense amplifier, regolatori di tensione,.. che necessitano di una corrente continua per funzionare. (è ad esempio un problema nelle memorie)

- Electron-hole pair generation in depletion region of reverse-biased diodes

- Diffusion of minority carriers through junction

- For sub-50nm technologies with highly-doped pn junctions, **tunneling through narrow depletion region** becomes an issue

Strong function of temperature

Much smaller than other leakage components in general

## Other sources of static power dissipation

- Circuit with dc bias currents:

sense amplifiers, voltage converters and regulators, sensors, mixed-signal components, etc

Should be turned off if not used, or standby current should be minimized

## Summary of Power Dissipation Sources

$$P \sim \alpha \times (C_L + C_{CS}) \times V_{swing} \times V_{DD} \times f + (I_{DC} + I_{Leak}) \times V_{DD}$$

- $\alpha$  – switching activity

- $C_L$  – load capacitance

- $C_{CS}$  – short-circuit capacitance

- $V_{swing}$  – voltage swing

- $f$  – frequency

- $I_{DC}$  – static current

- $I_{leak}$  – leakage current

$$P = \frac{\text{energy}}{\text{operation}} \times \text{rate} + \text{static power}$$

Potenza statica

Potenza dinamica con :

- alfa = switching activity

-  $C_L + C_{CS}$  (somma delle capacità della linea e di sc)

Mod by Giorgio Fissore, pag 25

## Model not Appropriate Any Longer

Traditional scaling model

If  $V_{DD} = 0.7$ , and  $\text{Freq} = \left(\frac{1}{0.7}\right)$ ,

$\text{Power} = CV_{DD}^2 f = \left(\frac{1}{0.7} \times 1.14^2\right) \times (0.7^2) \times \left(\frac{1}{0.7}\right) = 1.3$

Maintaining the frequency scaling model

If  $V_{DD} = 0.7$ , and  $\text{Freq} = 2$ ,

$\text{Power} = CV_{DD}^2 f = \left(\frac{1}{0.7} \times 1.14^2\right) \times (0.7^2) \times (2) = 1.8$

While slowing down voltage scaling

If  $V_{DD} = 0.85$ , and  $\text{Freq} = 2$ ,

$\text{Power} = CV_{DD}^2 f = \left(\frac{1}{0.7} \times 1.14^2\right) \times (0.85^2) \times (2) = 2.7$

## The New Design Philosophy

- Maximum performance (in terms of propagation delay) is too power-hungry, and/or not even practically achievable

- Many (if not most) applications either can tolerate larger latency, or can live with lower than maximum clock-speeds

- Excess performance (as offered by technology) to be used for energy/power reduction

Un progetto sarà tanto più buono, quanto più riesco a mediare tra questi due parametri.

Trading off speed for power

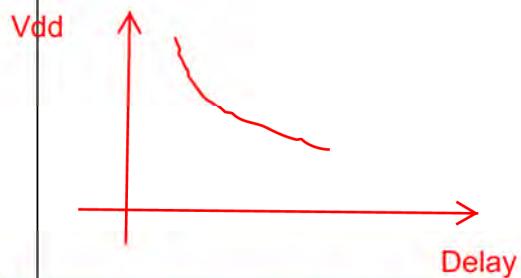

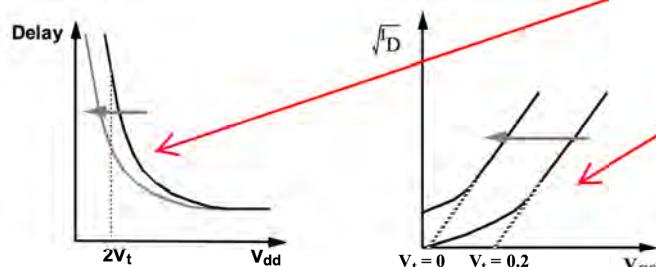

## Relationship Between Power and Delay

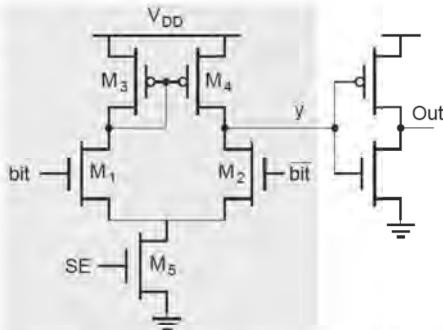

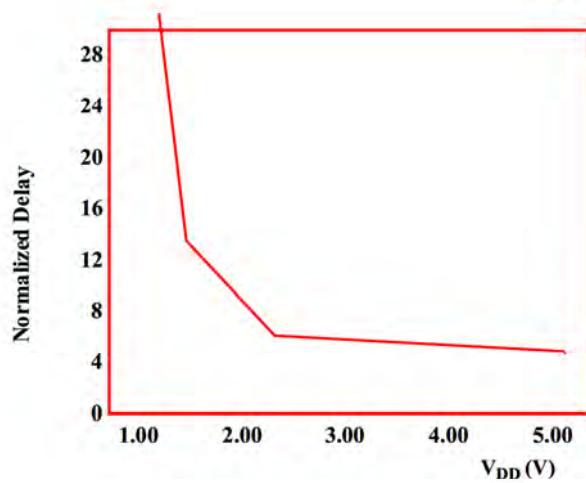

For a given activity level, power is reduced while delay is unchanged if both  $V_{DD}$  and  $V_{TH}$  are lowered such as from A to B.

-Aumentare la tensione di alimentazione fa crescere quadraticamente il consumo.

- Aumentare la tensione di soglia fa crescere esponenzialmente il consumo

Il ritardo invece dipende da quanto sono distanti la  $V_t$  e la  $V_{DD}$ . I punti A e B qui si trovano in punti di uguale ritardo; se però li guardiamo sul piano del consumo, si vede come tra i due punti ci sia una grande differenza. Ho quindi bisogno di tecnologie che mi permettano di scegliere la  $V_t$  per ottimizzare il legame tra  $V_t$  e  $V_{DD}$

Mod by Giorgio Tissore, pag 27

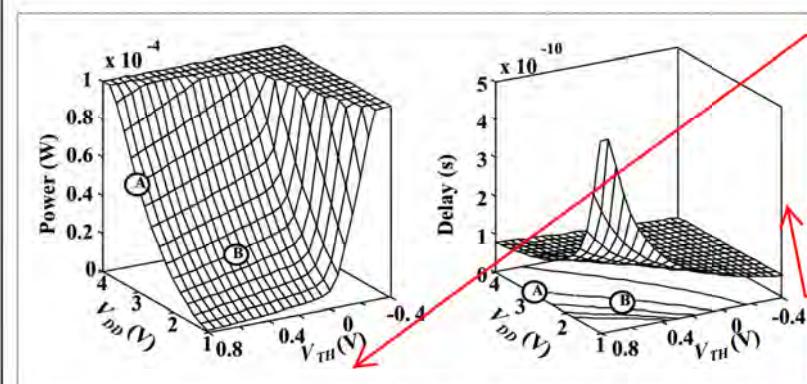

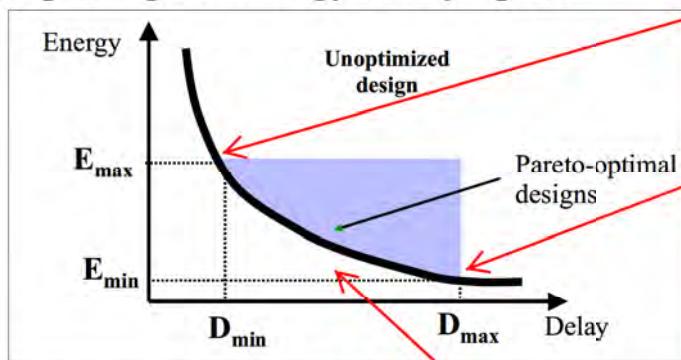

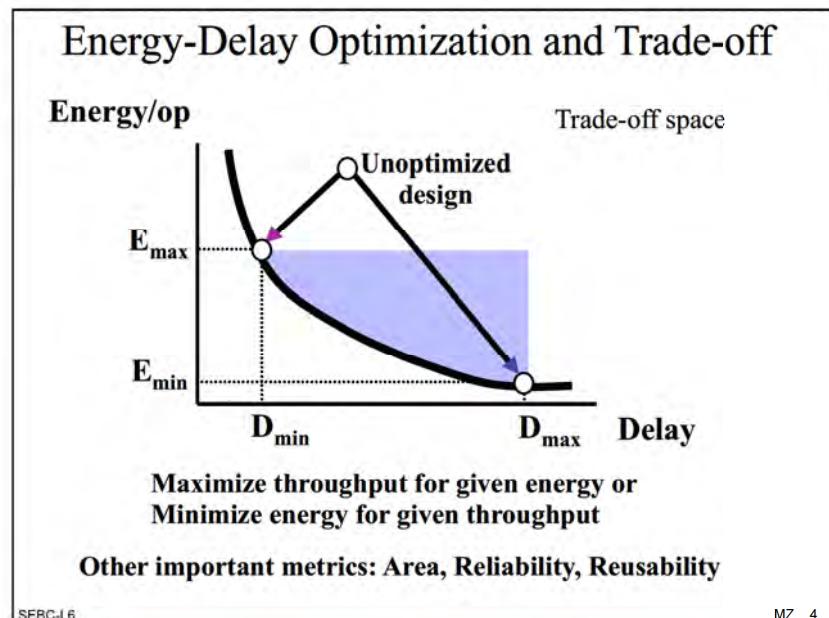

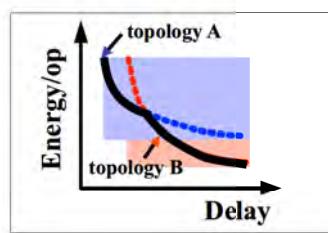

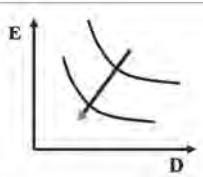

## Exploring the Energy-Delay Space

In energy-constrained world, design is trade-off process

- ♦ Minimize energy for a given performance requirement

- ♦ Maximize performance for given energy budget

SEBC-L2

[Ref: D. Markovic, JSSC'04]

MZ 34

Punto "lavora alla max frequenza con questa energia disponibile"

Punto "lavora consumando la minima energia avendo questo come massimo ritardo"

Questa curva limite (iperbole) è il minimo di energia-ritardo e rappresenta il punto massimo fino a cui posso portare il circuito.

Posso però avere vincoli legati ad energie e ritardi min/Max in cui posso spostarmi.

Es: "io ti do questa energia massima; vai a fare un progetto che la sfrutti, e che riesca ad avere il minimo ritardo possibile"

oppure "la macchina deve andare a 100Mhz, fai le tue scelte architettoniche in maniera che la tua macchina consumi meno possibile".

## Summary

- Power and energy are now primary design constraints

- Active power still dominating for most applications

- Supply voltage, activity and capacitance the key parameters

- Leakage becomes major factor in sub-100nm technology nodes

- Mostly impacted by supply and threshold voltages

- Design has become energy-delay trade-off exercise!

SEBC-L2

MZ 35

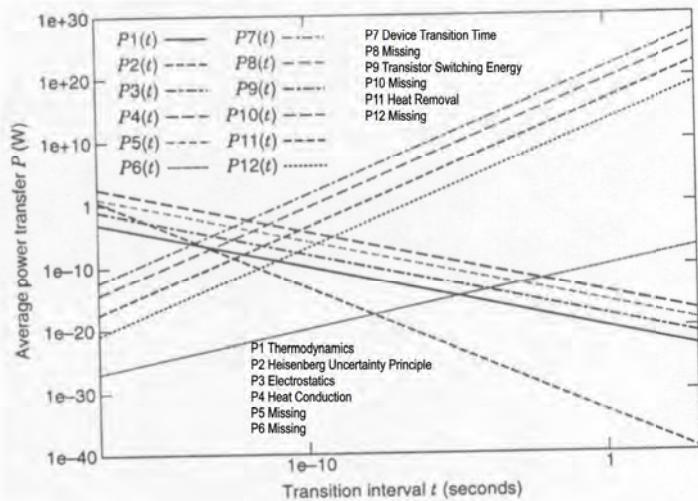

## Limits to Low-Power Design

- Moore's Law: # Transistors/chip grows 1.5 X every year

- Power-delay product ( $P t_d$ ) declined by  $1/10^5$  since late 1940's

- Limits to low-power design:

- Fundamental

- Material

- Device

- Circuit

- System

- Practical considerations

Mod by Giorgio Fissore, pag 29

SEBC-L2

MZ 36

## Material Limits

- Independent of devices and circuits

- Consider semiconductor cube of undoped material of dimension  $\Delta x$ , embedded in 3D matrix of such cubes

- Limit on switching energy and time (P3) calculated in terms of electrostatic energy stored in cube and transit time of a carrier through the cube:

- $P = \frac{1}{2} \epsilon_m E_c^2 \sigma_s^3 t_d^2$

- $\sigma_s$  = carrier saturation velocity

- $E_c$  = self-ionizing electric field strength

- $t_d$  = cube transit time

SEBC-L2

MZ 40

## Material Limits (cont'd)

- Heat removal consideration (P4): Fourier's Law of heat conduction

- $P = \pi K \sigma_s \Delta T t_d$

- $K$  = thermal conductivity of semiconductor,  $A$  = surface area of heat flow,  $\Delta T$  = temperature gradient

- For Si,  $P/t_d = 0.21 \text{ W/ns}$

- For GaAs,  $P/t_d = 0.69 \text{ W/ns}$  (unsuitable: even if faster needs to conduct more than 3 times as much heat for  $t_d$ )

- Silicon-on-Insulator (SOI):  $K_{eq} = 0.029 K_{Si} 0.02 K_{Si} 0.013 K_{Si}$  (most suitable)

SEBC-L2

MZ 41

## Material Limits (concluded)

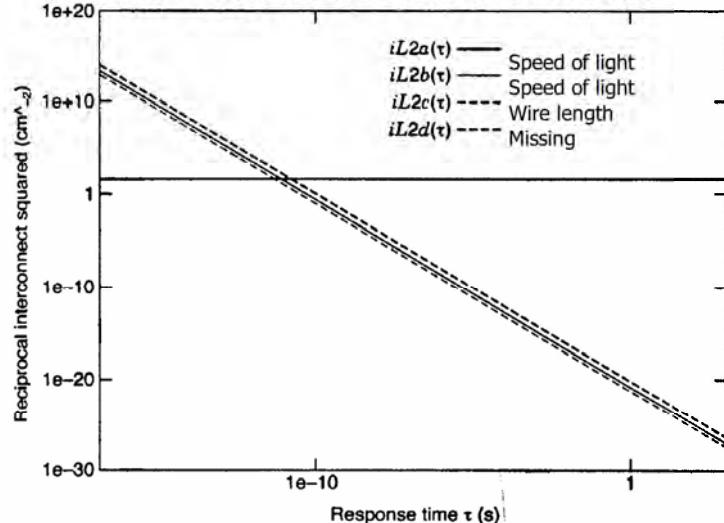

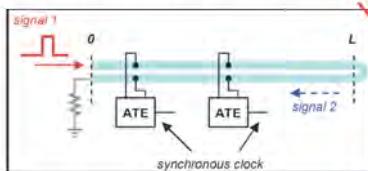

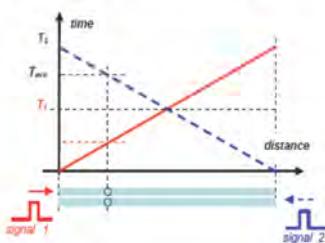

- Interconnect material limit (speed-of-light) ( $iL2b(\tau)$ ):

- Propagation time through interconnect of length  $L$  of a material with relative dielectric constant  $\epsilon_r$  must be:

$$t_d \geq \frac{L}{c_0 / \sqrt{\epsilon_r}}$$

Mod by Giorgio Fissore, pag 31

SEBC-L2

MZ 42

## Circuit Limits (concluded)

- Global interconnect limit (corner to corner) ( $iL2c(\tau)$ ):

- Response time:

- $\tau = (2.3 R_{tr} + R_{int}) C_{int}$

- $R_{int}$  = Total resistance of interconnection

- $R_{tr}$  = Output resistance of driver,

- $R_{int} < 2.3 R_{tr}$  to neglect delay due to wiring resistance

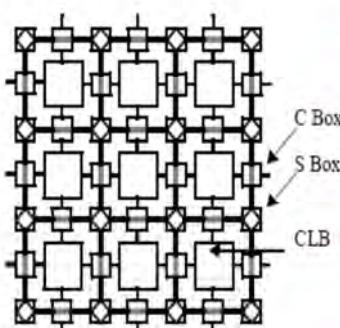

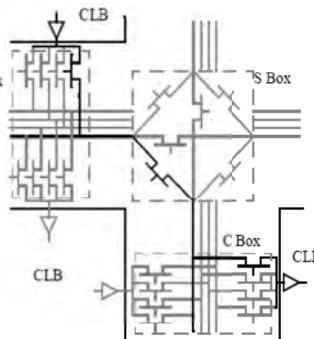

## System Limits

- Chip architecture

- Power-delay product of CMOS technology for the chip

- Heat removal capacity of chip package (50 W/cm)

- Clock frequency

- Chip physical size

- Selected architecture (only as an example):

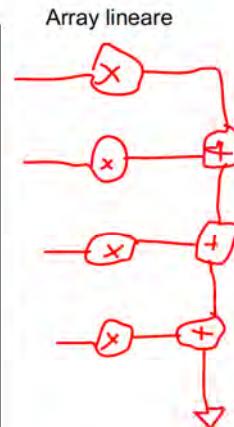

- Systolic array of 1024 identical square macrocells, each one of dimension  $L$

- 5-Level clock distribution H-tree

- Maximum Manhattan distance for clock within macrocell is  $L$ , for logic signal it is  $2L$

## System Limits (cont'd)

- Limit on logic gate dimension:

$$[A_{rl}]^{1/2} = \overline{R}_{rl} M \frac{p_w}{e_w n_w}$$

$\overline{R}_{rl}$  = average length of the interconnections

- Gate logic area is logic limited for  $n_w = 4$  (# wiring levels),

$p_w = 0.2 \text{ mm}$  (wiring pitch),  $e_w = 0.75$  (wiring efficiency factor)

$\overline{R}_{rl} = 6$ ,  $M = 3$  (*fanout of gate*), and for other values

$$t_d = t_{drl} + \frac{T_{cc}}{n_{cp}} \quad T_{cc} = \text{corner to corner response time}$$

$n_{cp}$  = critical path delay

(effective propagation delay of the composite gate)

Mod by Giorgio Fissore, pag 33

## P Limits Plotted

SEBC-L2

MZ 52

## Interconnect Limits Plotted

SEBC-L2

MZ 53

Mod by Giorgio Fissore, pag 35

## Why power estimation is necessary

- Determining realistic power requires accurate (i.e. switch-level or below) simulation of the final implementation of a design.

- Infeasible for complex circuits.

- Similar to timing analysis but:

- Complex relation with other quantities (e.g. circuit capacitance).

- More difficult to evaluate.

- Power estimators are not just simulators!!!!

## Power Estimation Issues

- Power estimation implies estimation of:

- Switching activity.

- Capacitance.

$$P = Esw \cdot f \cdot C \cdot V_{dd}^2$$

- Different expectations depending on the level of abstraction:

- Low-levels:

- Absolute figures

- Accuracy

- Design Validation

- High-levels:

- Relative figures

- Estimation time !!!!!!!

- Design exploration !!!!!

A livello basso, voglio che quando dalla libreria prendo es il full adder, sappia esattamente quanto consuma.

L'analisi a livello basso dev'essere molto precisa, fino al  $\mu$ W, e ciò è fattibile poichè gli oggetti sono piccoli

A livello più alto invece mi va bene una cosa più approssimativa, es quanto consumo se metto una seconda ALU?

## Gate-level Power Estimation

- Modeling issues

- Delay models

- Spatial and temporal correlations

- Signal feedback (sequential circuits)

- Estimation methods:

- Simulation-based

- Probabilistic

- Statistical

Partiamo da LIV BASSO

Devo modellare il circuito, facendo sì di avere un modello facilmente utilizzabile (cambiano gli ingressi >> prevedo facilmente le uscite).

Dovrò modellizzare questi tre parametri.

Potrò formularli con questi tre metodi (probabilistico quasi mai usato, e statistico più diffuso)

## Real-delay Model

- Real delay mode implies:

1. Different pin-to-pin delays

2. Different rise and fall delays

3. Gates with inertial delays (Input values before and after the input transition must be stable for a time at least equal to the delay of the gate)

- 1 and 2 may increase the amount of switching

- 3 may decrease the amount of switching (some transitions are filtered)

- Because of opposite changes, error may cancel

- Unit-delay model estimates are roughly 10 to 15 % smaller, on average

Come se il gate avesse una certa banda, tutti i segnali che arrivano a frequenza più alta non passano

SEBC-L3

MZ 10

## Correlations:

### ■ Spatial correlation:

Two signals are not independent in the same clock cycle

#### ■ Sources:

- Structural signal dependencies due to reconvergent fanouts.

- Input pattern dependencies due to particular sequences of inputs.

### ■ Temporal correlation:

The values assumed by a signal in two consecutive clock cycles are not independent.

#### ■ Sources:

- Feedback in sequential circuits

- Input pattern dependencies due to particular sequences of inputs

E' più preciso, ma anche molto più lungo da calcolare.

Cmq il fatto che 1 e 2 possano aumentare gli switch e 3 li abbassi (non lasciando passare alcuni glitch) si bilanciano abbastanza.

Si usa perciò, la maggior parte delle volte, il modello a unit delay per fare simulazioni.

Calcolare in modo probabilistico il consumo delle porte non è affatto facile, poichè non si possono nemmeno considerare i vari elementi del circuito come stocasticamente indipendenti; vi sono infatti sia correlazioni spaziali, sia temporali.

Questo porta il modello probabilistico ad essere esageratamente complicato (ingestibile)

SEBC-L3

MZ 11

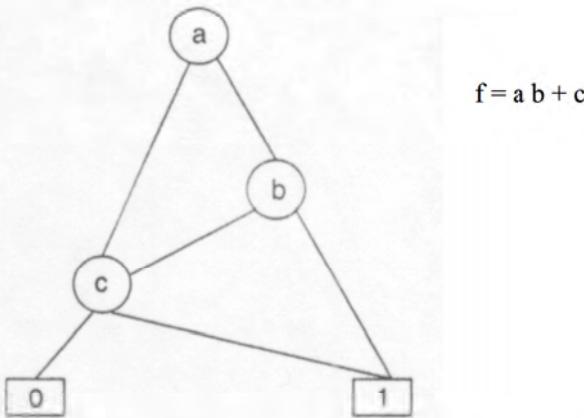

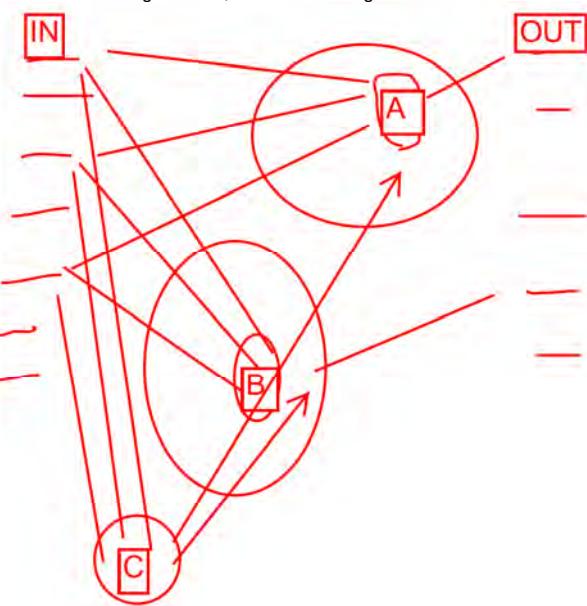

## Problem: Reconvergent Fanout

Reconvergence

$$P(Z=1) = P(B=1) \times P(X=1 | B=1)$$

Becomes complex and intractable real fast

Mod by Giorgio Fissore, pag 39

SEBC-L3

MZ 12

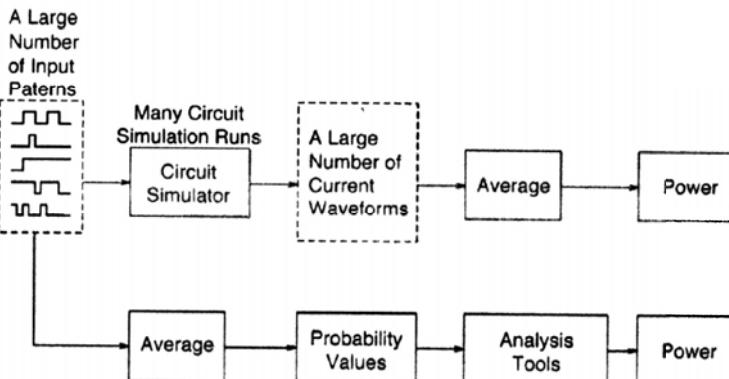

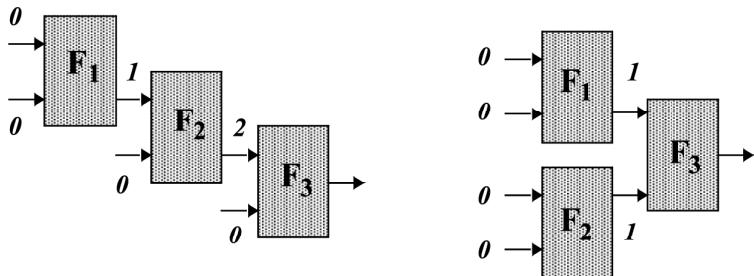

## Flows for Power Estimation

SEBC-L3

MZ 16

## Simulation-Based Methods

- Based on the simulation of input patterns.

- Also called *dynamic*

- Simplified solutions:

- Assume same supply voltage throughout the whole chip.

- Reduce the problem to that of estimating the power supply currents drawn by the components.

- Logic simulation can be used to estimate the currents.

- Strongly pattern-dependent

Questo metodo è fortemente dipendente dall'accuratezza dei pattern in ingresso; la difficoltà sta proprio nel trovare buoni vettori di ingresso. Se buona funziona bene, altrimenti rischia di non essere accurato.

SEBC-L3

MZ 17

## Simulation-Based Methods

- Advantages:

- Use accurate models (i.e. timing, power) of state-of-the-art circuit simulators (e.g. SPICE).

- Very accurate estimates

- Disadvantages:

- Require complete information about input patterns (exhaustive input pattern simulation).

- Very costly in time => applicability limited to small circuits

- Mainly used for design validation.

Mod by Giorgio Fissore, pag 41

SEBC-L3

MZ 18

## Probabilistic Methods: Definitions

- The starting hypothesis is that the system is a synchronous one, with a clock signal that controls all the internal activities (one transition/clock cycle).

- Signal probability  $p^x(n)$  of node  $n$  : average fraction of clock cycles (!!!) in which the steady state of  $n$  is  $x$

- Transition probability,  $p^{ij}(n)$  of node  $n$  : average fraction of clock cycles in which the steady state of  $n$  changes from  $i$  to  $j$ .

- Switching activity,  $Esw(n)$  or  $A(n)$  of node  $n$  : expected number of transitions at  $n$  per clock cycle.

$p^x(n) = \#$ medio di CLK in cui il segnale vale 1

$p^{ij}(n) = \#$ medio di CLK in cui lo stato di  $n$  cambia da  $i$  a  $j$

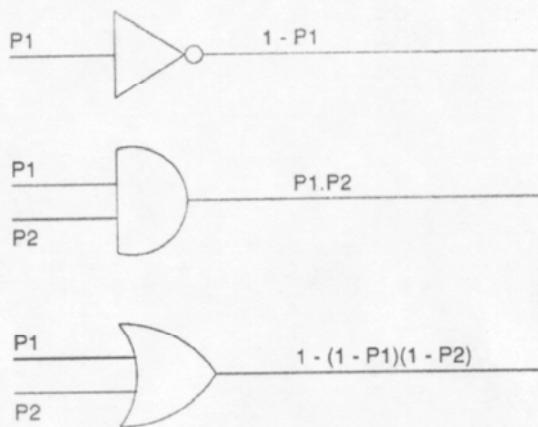

## Computing Signal Probabilities

- Output probability of a basic boolean function is calculated with standard probabilistic theory

- for an AND gate, if inputs have  $P1$  and  $P2$  signal prob. the output will have  $P(\text{out}) = P1 \cdot P2$

- for an OR gate, the output will have

$$P(\text{out}) = 1 - (1 - P1)(1 - P2)$$

(the probability to have a 1 as output is equal to 1 less the product of the probabilities to have both inputs at 0)

## Example Signal Probabilities

Se non considero i problemi della riconvergenza e della correlazione, se mi calcolo le probabilità dei segnali per le varie porte, sono in grado di calcolarmi la  $Esw$  in ciascun punto del circuito

Mod by Giorgio Fissore, pag 43

## Statistical methods

- Advantages:

- Fast

- Can manage large circuits

- Desired degree of accuracy as a function of # of measurements

- No special arrangements for sequential circuits (although a different convergence criterion may be required).

- Disadvantages:

- Gaussian assumption may be wrong for some circuits

- For some input sequences # of measurements may be large

- Not suitable for computing power of individual gates.

SEBC-L3

MZ 28

## Parker-McCluskey Signal Probability Calculation Algorithm

(algoritmo per il calcolo delle prob che tiene conto anche della riconvergenza - anki se cmq non lo useremo-)

- Signal probabilities are used to accurately estimate signal activity

- It is essential to accurately calculate signal prob. for further use in estimating *activity*

- A general algorithm, proposed by Parker and McCluskey is widely used for a generic system (no requirements on clock regime..... also purely combinatorial !!!!!!!)

SEBC-L3

MZ 29

## Parker-McCluskey Signal Probability Calculation Algorithm

- Inputs: Signal probabilities of all circuit inputs

- Outputs: Signal probabilities of all circuit nodes

- Step 1: Assign a variable for each input and logic gate

- Step 2: Going from inputs to outputs, compute symbolic probability of each gate output

- Step 3: Suppress all exponents in symbolic expressions

Premise: Reconvenger fanouts make signals correlated, and higher-order powers of probabilities cannot be present in symbolic expressions when primary inputs are independent (intuitively....)

Forse "ogni volta che trovi esponenti cancella" o qlcs del genere

Mo... pag 45

SEBC-L3

MZ 30

## Binary Decision Diagram to Calculate Signal Probability

- Traverse *Binary Decision Diagram* (BDD) from root in depth-first traversal, with post-order evaluation of  $P(\cdot)$  at every node, to determine:

- $P(f) = P(x_1)P(f_{x_1}) + P(\bar{x}_1)P(f_{\bar{x}_1})$

### Example BDD

the tree rooted to the left of  $a$  represents  $\bar{f}a$ ; the right.....  $f_a$

## Estimating Signal Activity

- Probabilistic techniques:

- Boolean Difference (Sellers):

- Symbolic Boolean method to calculate signal activity (see notes)

- Requires an *Extended State Transition Graph* (ESTG) to calculate activities for sequential circuits

- Use Chapman-Kolmogorov Equations

- Markov Probabilistic Process Model

- Need to use an approximate solution method – exact method is too slow

- Approximate method is exact for tree-structured pipelined circuits

- Only gives lower-bound on activity, because the method ignores glitching power

- Due to use of zero-delay logic simulation model

- Inactive circuit parts still contribute inordinately to power estimate

- Due to assumption that even turned-off inputs have 0.5 prob.

Mod by Giorgio Fissore, pag 47

## Simultaneous Switching Problems

- The method works theoretically with ALL the clocking regimes (also combinational only regimes!).

- The method shown fails in case of simultaneous switching of inputs.

- A new algorithm, based on Generalized Boolean Difference, can be used to consider this condition (see book... a lot of mathematics....and logic...).

**PROBLEMA!!**

questo metodo si perde tutte le commutazioni multiple ed in più, come visto prima, non prende tutti (gli switch? i glitch?).

E' un metodo quindi assolutamente deficitario.

SEBC-L3

MZ 40

## Simultaneous Switching Problems

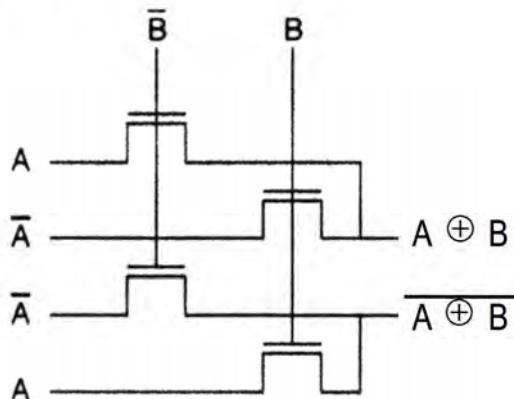

Figure 3.6 Signal activities for XOR logic.

SEBC-L3

MZ 41

## Simultaneous Switching Problems

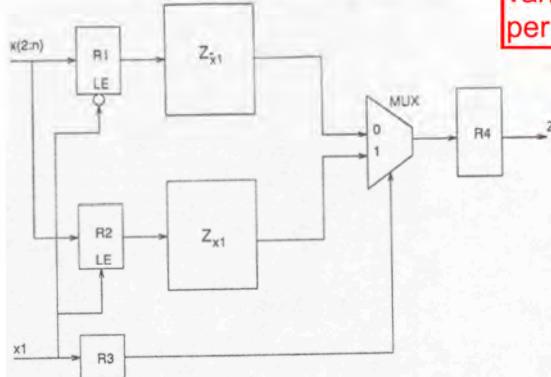

- A different approach can be used for the majority of digital systems;

- Suppose to have a synchronous clock ( fck ) system where combinational paths are inserted between latches.

Mod by Giorgio Fissore, pag 49

SEBC-L3

MZ 42

## Circuit function

- The probability for the output to make a transition is given by the probability than the current state is 0 times the probability that the next state is 1 *plus* the probability than the current state is 1 times the probability that the next state is 0.

- As a consequence:

$$Esw = (p(O=0)p(O=1) + p(O=1)p(O=0)) = 3/8$$

## Circuit function

- Example: 2-input XOR static CMOS gate:

$O = \text{XOR}(A, B)$

- Assume only one input transition per clock cycle (synchronous clock system!!!)

- Inputs are equiprobable:  $p(A=1) = p(B=1) = 1/2$

- The probability for the output to 1 is

$$p(O=1) = (1-p(A=1))p(B=1) + (p(A=1))(1-p(B=1)) = 1/2$$

$$p(O=0) = 1 - p(O=1) = 1/2$$

## Circuit function

- The probability for the output to make a transition is given by the probability than the current state is 0 times the probability that the next state is 1 *plus* the probability than the current state is 1 times the probability that the next state is 0.

- As a consequence:

$$Esw = (p(O=0)p(O=1) + p(O=1)p(O=0)) = 1/2$$

- The  $Esw$  probability that the output switches heavily depends on the circuit function!!!!

Mod by Giorgio Fissore, pag 51

## Circuit Technology

- Example: 2-input NOR Dynamic CMOS gate:

$O = \text{NOR}(A, B)$

- Assume only one input transition per clock cycle (synchronous clock system!!!)

- Inputs are equiprobable:  $p(A=1) = p(B=1) = 1/2$

- The probability for the output to be discharged is:

$p(O=0) = 3/4$

- Therefore the probability for  $C_L$  to be re-charged at the next clock cycle equals  $p(O=0)$

## Transition Probabilities for Dynamic Gates

|             | $P_{0 \rightarrow 1}$          |

|-------------|--------------------------------|

| <b>AND</b>  | $(1 - P_A P_B)$                |

| <b>OR</b>   | $(1 - P_A)(1 - P_B)$           |

| <b>EXOR</b> | $(1 - (P_A + P_B - 2P_A P_B))$ |

Switching Activity for Precharged Dynamic Gates

$$P_{0 \rightarrow 1} = P_0$$

La tecnologia con cui realizzo le porte impatta pesantemente la Esw del mio circuito!!

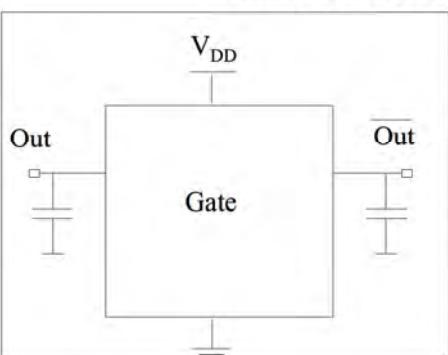

## Differential Logic?

Static:

Activity is doubled

Dynamic:

Transition probability

is 1!

Hence: power always increases.

Usando una logica differenziale l'attività risulta raddoppiata, se non ho grossi vantaggi, questa strada va quindi scartata

Mod by Giorgio Fissore, pag 53

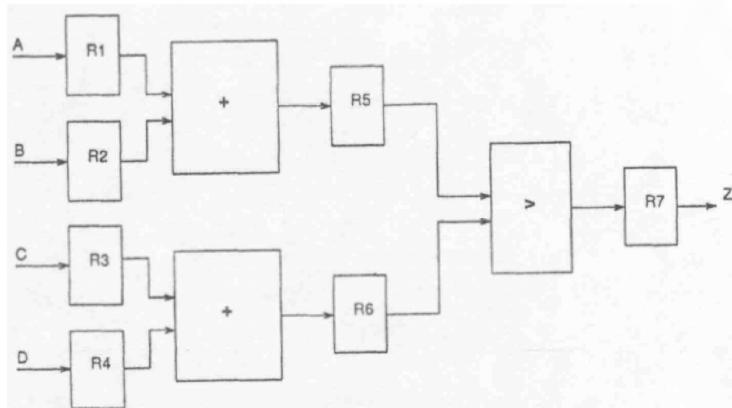

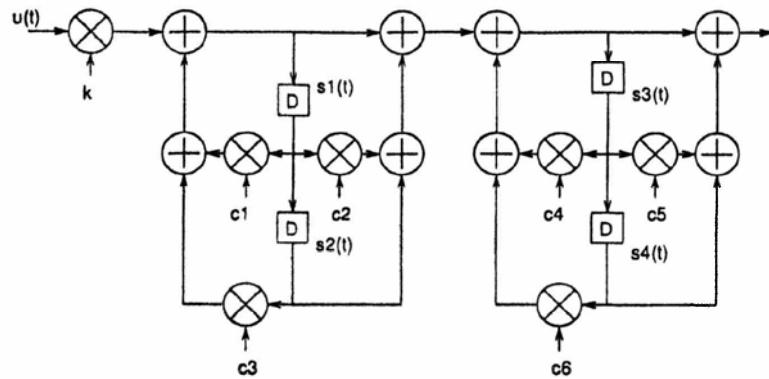

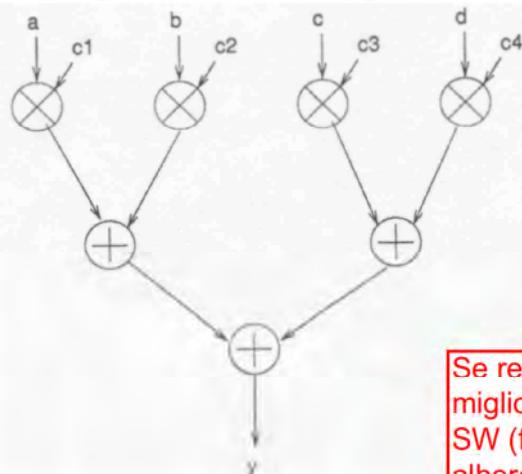

## Circuit Topology

- Tree Structure (Static CMOS gates):

$$O_1 = A \cdot B ; O_2 = C \cdot D ; O = O_1 \cdot O_2$$

- All inputs are equiprobable:

$$P(O_1=1) = 1/4 \quad P(O_1=0) = 3/4$$

$$P(O_2=1) = 1/4 \quad P(O_2=0) = 3/4$$

$$P(O=1) = 1/16 \quad P(O=0) = 15/16$$

$$E_{sw}(O_1) = 3/8 \quad \underline{E_{sw}(O_2) = 3/8}$$

$$E_{sw}(O) = 15/128$$

## Circuit Topology

- Timing skew between signals may cause spurious transitions resulting in extra power dissipation!!!

- The dynamic component of the switching activities is due to the glitches (next lectures...).

- These glitches can depend on the topology and relative delays: chain topology is less robust to skew as balanced tree, where the delay of each stage can be controlled to be similar (next slides).

- Dynamic CMOS gates are not affected by glitches, since each gate output can make at most one power consuming transition per clock cycle!!!

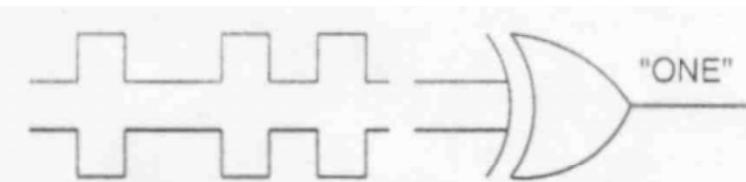

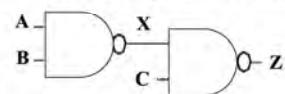

## Glitching in Static CMOS

also called: dynamic hazards

ABC 101 000

X

Z

Unit Delay

Observe: No glitching in dynamic circuits

Un glitch nella catena, si propaga per tutta la catena

Mod by Giorgio Fissore, pag 55

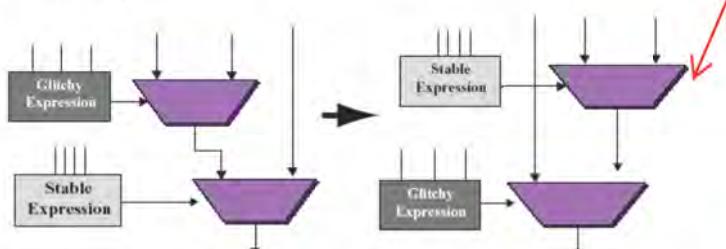

## How to Cope with Glitching?

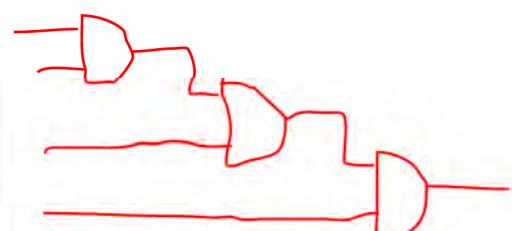

### Equalize Lengths of Timing Paths Through Design

SEBC-L3

MZ 64

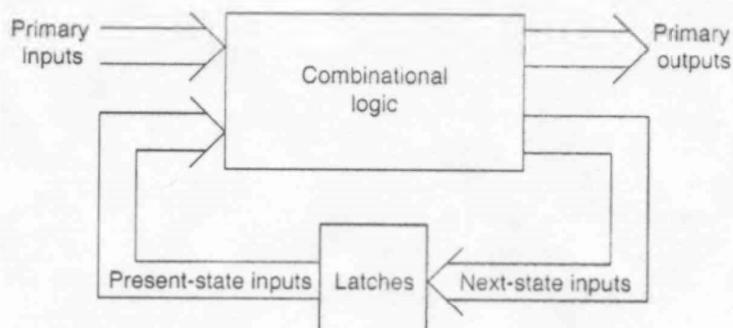

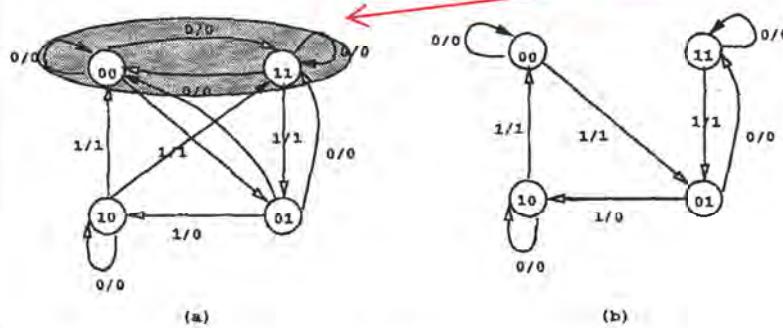

## Representing Sequential Circuits

SEBC-L3

MZ 65

## Representing Sequential Circuits

- Accurate power estimation is more difficult since signal prob. and activities at the state inputs are not known ahead.

- The prob. of being in different states must be determined in the steady state.

- Taking only spatial correlations of signals into consideration:

$P_i = [p_1..p_n]$  signal prob. of  $n$  independent primary inputs

$P_{out} = F(P_i, P_s)$   $i = \text{inputs}$ ,  $s = \text{state}$

$P_n = F'(P_i, P_s)$   $P_n = \text{signal prob. for next-state inputs}$

- In steady-state, noting that  $P_n = P_s$ , it is possible to solve the set of equations for state prob.

Nell'evoluzione della macchina ho una forte correlazione sia spaziale che temporale. Diventa quindi quasi impossibile fare dei calcoli probabilistici.

Mod by Giorgio Fissore, pag 57

SEBC-L3

MZ 66

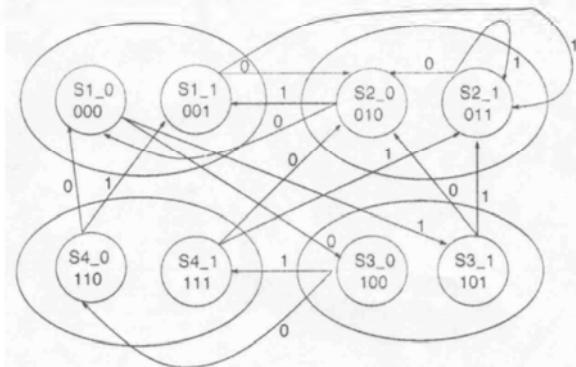

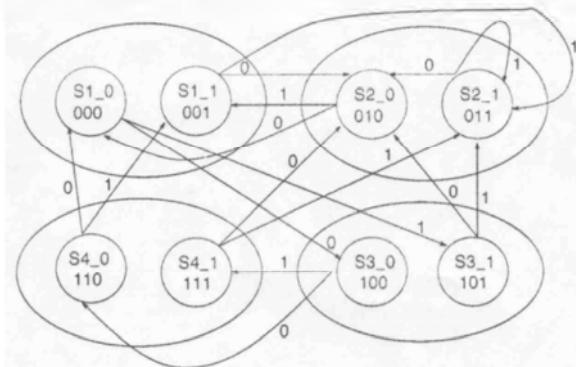

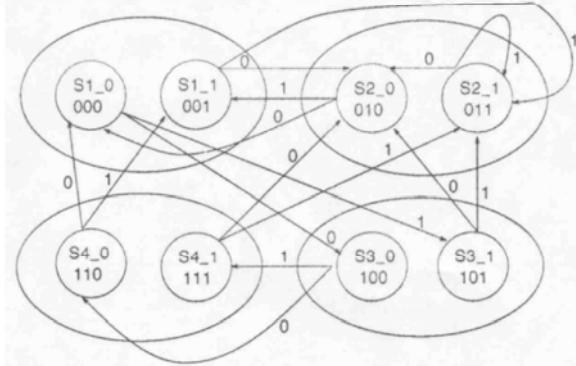

## Extended State Transition Graph

- Represent each state with 2 present state bits and one present input bit to facilitate correct prob. calculation (the variable on each edge is the next input (at time T))

SEBC-L3

MZ 70

"non vogliamo fare simulazioni".

Allora espando ogni singolo stato, mettendo nei nuovi sottostati anche i bit in ingresso (es stato s1 con bit\_ingr 1 e bit\_ingr 0).

Così non servirebbero simulazioni, ma il numero di stati esplode troppo in fretta.

## Extended State Transition Graph

- Each state is split in  $2^{**N}$  states, where N is the number of primary inputs

SEBC-L3

MZ 71

## Extended State Transition Graph

- State transitions do not depend on the history: signal probabilities and activities can be calculated....but..... for large FSM it becomes very CPU expensive!!!!

SEBC-L3

MZ 72

Mod by Giorgio Fissore, pag 59

## Why Is Correlation a Problem?

- $I^T$  and  $ns2^0$  appear to be independent

- No common ancestor node in graph

- But,  $ns2^0$  is topologically dependent on node  $I^0$  (input)

- $I^0$  and  $I^T$  are temporally correlated

- Gives erroneous power estimate unless we correct for this

- Define  $I$  as a temporally reconvergent node, rather than a topologically reconvergent node

SEBC-L3

MZ 76

## Summary of Power Estimation

- Probabilistic techniques: Not useful

- Only give lower-bound on activity, ignore glitching power

- Inactive circuit parts contribute inordinately to power estimate

- Major Problem – unable to estimate glitching power

- Probability theory needs to be augmented with Monte-Carlo analysis for power estimation

SEBC-L3

MZ 77

Mod by Giorgio Fissore, pag 61

## Necessary Relationships

- $|\bar{p} - P_{\text{avg}}| < \frac{t_{\alpha/2} s}{\sqrt{N}}$   $\frac{|\bar{p} - P_{\text{avg}}|}{\bar{p}} < \frac{t_{\alpha/2} s}{\bar{p}\sqrt{N}}$

- Required condition:  $\frac{t_{\alpha/2} s}{\bar{p}\sqrt{N}} < \epsilon$

- Required # simulations for desired confidence level:

$$N \geq \left( \frac{t_{\alpha/2} s}{\bar{p}\epsilon} \right)^2$$

- Sometimes need only 10 simulations to get accuracy

- CPU time comparable to probabilistic techniques

- May not accurately estimate power of individual gates that switch very infrequently

## Modification for Low-Activity Gates

- $n_i$ ,  $1 \leq i \leq N$ , # transitions at node during simulation  $i$

- $\bar{n} = n_i / N$  = average # transitions at node

- Close to normal distribution for large  $N$  (Central Limit Theorem of Statistics)

- $\beta$  = true expected value of ave. # node transitions

- $s$  = measured std. dev. of  $N$  values of  $n_i$

- $(1 - \alpha) \times 100\%$  = confidence level

- $z_{\alpha/2}$  obtained from normal distribution

## Necessary Relationships (Low-Activity)

$$\frac{\beta - \bar{n}}{\bar{n}} \leq \frac{z_{\alpha/2} s}{\bar{n}\sqrt{N}} \quad (3.33)$$

$$N \geq \left( \frac{z_{\alpha/2} s}{\epsilon \bar{n}} \right)^2$$

$$N \geq \left( \frac{z_{\alpha/2} s}{\epsilon \beta_{\min}} \right)^2$$

$$|\beta - \bar{n}| \leq \frac{z_{\alpha/2} s}{\sqrt{N}} \leq \beta_{\min} \epsilon$$

- Low-activity nodes take longest time to converge, have least effect on ave. power dissipation & circuit reliability

Mod by Giorgio Fissore, pag 63

## Problems with Example

- $G1 = \{s1\ s0, \overline{s1}\ \overline{s0}\}$  and  $G2 = \{\overline{s1}\ s0, s1\ \overline{s0}\}$

- $P(\text{transition between } G1 \text{ and } G2)$  is very low

- Near-closed state sets

- suppose  $y = \text{output} = (\overline{s1}\ \overline{s0} + s1\ s0) x1$

- Considering only  $G1$ ,  $y = x1$

- Considering only  $G2$ ,  $y = 0$

- Very different probability behavior for  $G1$  and  $G2$  sets

- Data sample set is *biased* – causes errors

## Removal of Biasing

- Must know  $P(G_1)$  and  $P(G_2)$

- Compute normalized activity:

- $a(y) = P(G_1) X a(y, G_1) + P(G_2) X a(y, G_2)$

- May assume that PIs are temporally uncorrelated (could be wrong) or that they are Markov (future value depends only on present value and not on the past)

- With Markov assumption, can implicitly compute  $P(G_1)$  and  $P(G_2)$

- Transform STG into ESTG that is Markov

- $P_{\text{warmup}}^k$  is probability of reaching  $G_i$  after  $k$  clock cycles with any initial state

- $|P_{\text{warmup}}^k(G_i) - P(G_i)| \leq N_s |\lambda_2|^k$

- $\lambda_2$  is second-largest eigenvalue of transition matrix

- $N_s = \# \text{ESTG states}$

## Removal of Biasing (concluded)

- $k = \# \text{clock cycles needed for warmup}$

$$k \geq \frac{\ln[N_s/\epsilon_G P(G_i)]}{\ln 1/\lambda_2} \quad (3.39)$$

- Repeat Procedure  $N$  times, and take mean of samples

$$\begin{aligned} & \frac{\left( \sum_{j=1}^{N \cdot P(G_1)} a_j(y|G_1) + \sum_{j=1}^{N \cdot P(G_2)} a_j(y|G_2) \right)}{N} \\ &= \frac{N \cdot P(G_1) a(y|G_1) + N \cdot P(G_2) a(y|G_2)}{N} \\ &= P(G_1) a(y|G_1) + P(G_2) a(y|G_2) \end{aligned}$$

Mod by Giorgio Fissore, pag 65

## Three-Valued Logic Simulation

Used by logic simulators to model static hazards

In the table AND values calculated according to the possible hazard (X)

| AND | 0 | 1 | X |

|-----|---|---|---|

| 0   | 0 | 0 | 0 |

| 1   | 0 | 1 | X |

| X   | 0 | X | X |

SEBC-L4

MZ 16

Modo più semplice per simulare in maniera logica i glitch (ma non usati), logica a tre stati, con il terzo X che rappresenta il glitch.

## Six-Valued Logic Simulation

- $t'$  is time instant in between  $t$  and  $t + 1$  to detect static hazards

Metodo utilizzato effettivamente dai simulatori; tiene conto di glitch statici.

| Logic Representation | Bit Sequences at $t, t', t + 1$ |

|----------------------|---------------------------------|

| 0—Static 0           | 000                             |

| 1—Static 1           | 111                             |

| R—Rising             | 0U1                             |

| F—Falling            | 1U0                             |

| SH0—Static 0 hazard  | 0U0                             |

| SH1—Static 1 hazard  | 1U1                             |

SEBC-L4

MZ

U = undefined

Possiamo così verificare, ad esempio l'effetto di un glitch statico 0>1 all'interno della nostra catena di AND, metodo pessimistico (buona cosa perchè vogliamo sapere quanto consuma al max) poichè si ipotizza che se c'è la possibilità che ci sia un glitch, questo ci sia effettivamente.

## Six-Valued Logic for AND Gate (Pessimistic)

- Truth table of the logic simulations for the 6-valued logic;

- Pessimistic since some hazards might not be present under certain delay conditions

| AND | 0 | 1   | R   | F   | SH0 | SH1 |

|-----|---|-----|-----|-----|-----|-----|

| 0   | 0 | 0   | 0   | 0   | 0   | 0   |

| 1   | 0 | 1   | R   | F   | SH0 | SH1 |

| R   | 0 | R   | R   | SH0 | SH0 | R   |

| F   | 0 | F   | SH0 | F   | SH0 | F   |

| SH0 | 0 | SH0 | SH0 | SH0 | SH0 | SH0 |

| SH1 | 0 | SH1 | R   | F   | SH0 | SH1 |

Mod by Giorgio Fissore, pag 67

SEBC-L4

MZ 18

## Nominal Balanced Path Delay Models

Vediamo come i ritardi influenzano i glitch, in due immagini a 1) ritardo fisso 2) ritardo non costante (pag dopo)

SEBC-L4

MZ 22

## Tree-Structured Random Delay Variations in Circuit

- Unfortunately gate delays may have variations

- As a consequence glitches occur and the activities in individual nodes change (possibly increasing!!!)

- To capture this random behavior, the sources of uncertainty are represented by probability distributions.

SEBC-L4

MZ 23

## Tree-Structured Random Delay Variations in Circuit

Addirittura più di una commutazione per colpo di CLK

Tanto più la tecnologia si rimpiccolisce, tanto più aumenta la distribuzione dei parametri (fondamentale sotto i 30 nm dove la dispersione è talmente vasta che non ha più senso parlare di valori tipici)

Mod by Giorgio Fissore, pag 69

SEBC-L4

MZ 24

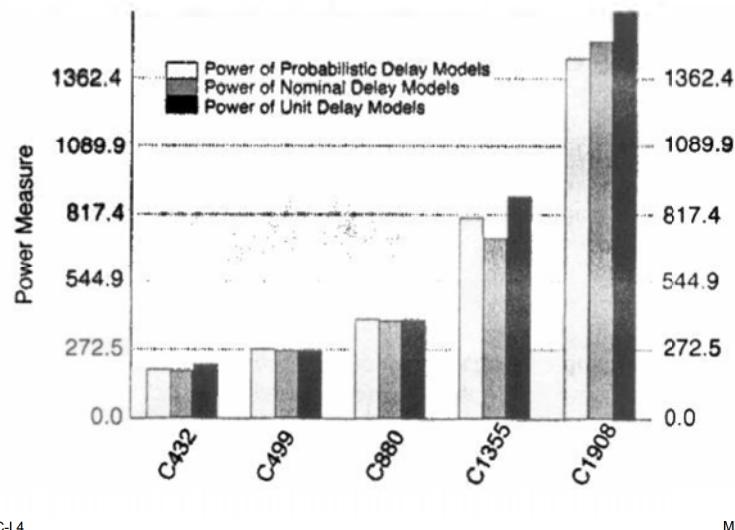

## Relative Dynamic Power

SEBC-L4

MZ 28

## Power with Different Delay Models

SEBC-L4

MZ 29

## Sensitivity Analysis

- Monte-Carlo methods are accurate if exact probabilities and activities are available for PIs

- Should represent average power dissipation as a range  $[\text{Power}_{\min}, \text{Power}_{\max}]$

- Takes 2.3 CPU s to do one symbolic simulation for c432 – need to do  $2^{36}$  simulations to cover all input cases (impractical... more than 5000 years!)

- Use power sensitivities instead

PI: Primary Input

Mod by Giorgio Fissore, pag 71

SEBC-L4

MZ 30

## Power Estimation via Vector Compaction

- Work of Tsui, Marculescu, Marculescu, and Pedram

- Method: Generate compact vector set that represents the original vector set, but takes much less time to simulate

- Given vector sequence  $S_1$  of length  $L_1$  with property  $P_1$ , generate a much shorter sequence  $S_2$  of length  $L_2$  with similar property  $P_2$  and use it to estimate power

- Properties  $P_1$  and  $P_2$  are the pair-wise transition probabilities among all possible input combinations

- Compacted the sequence 20 times, while keeping power estimation error within 5 %

SEBC-L4

MZ 34

## Summary of Power Estimation

- Probabilistic techniques: Not useful

- Only give lower-bound on activity, ignore glitching power

- Inactive circuit parts contribute inordinately to power estimate

- Statistical techniques: Useful

- Repeatedly simulate circuit with logic simulator, noting node activities

- Randomly-generated inputs

- Statistical mean estimation techniques with Monte Carlo simulation

- Glitching Power estimated by Monte Carlo methods + probabilistic delay

- Power Sensitivity used to estimate min. and max. average power

- Power estimated with input vector compaction or information theory

Unico metodo compatibile con l'utilizzo durante il progetto dell'architettura.

(faccio il progetto, simulo, modifco, controllo se meglio o peggio).

SEBC-L4

MZ 35

## Gate-Level Power Estimation: Summary

- Essential factors to capture for accurate logic-level power estimation:

- Delay models

- Signal correlations

- Available techniques guarantee very low estimation errors:

- Three main classes of methods:

- Simulation-based

- Probabilistic

- Statistical

- At this level, other metrics can be estimated (e.g. peak power)

Così si chiude la stima di potenza a livello gate; va però ricordato che per arrivare a questo livello, bisogna prima passare per la sintesi, e questa può richiedere qualche ora.

Passo allora alla valutazione al livello dei registri RTL, che mi permette di fare una valutazione presintesi.

Mod by Giorgio Fissore, pag 73

SEBC-L4

MZ 36

## RTL-Level Power Estimation

- Analytical models relate power dissipation to physical quantities to express activity and capacitance:

- Best suited for:

- Black-box estimates (no data are available for individual blocks).

- Fixed structure components, e.g. memories.

- Empirical models are based on a measure of power, from which a model is built:

- Best suited for library-based approaches.

- Can be built for custom functional blocks, as long as some real power figures are available (e.g. taken from previous implementations).

Metodi analitici, non usati, cercano di tirare fuori una qualche equazione (funzionano meglio per strutture estremamente ripetitive es memorie, o si usa in black box, dove non ho nessun'altra possibilità)

Utilizziamo questo

## Analytical Complexity-Based Methods

- Complexity is used as capacitance estimate.

- *Complexity = Equivalent gate count*

- Power of a block is roughly estimated as:

$$P = (\# \text{ of equivalent gates}) P_{\text{gate}}$$

- Limitations:

- Based on power consumption of a reference gate

=> No account for circuit implementation or clocking strategy.

- Fixed, static *activity factor* assumed.

## Analytical Activity-Based Methods

- Activity is regarded as dominant factor of power consumption.

- Models are based on information-theory concepts: exploit correlation between activity and *entropy*.

- Abstract power model:

$$P = 1/2 f V_{dd}^2 C(H) S(H)$$

- Use entropy H to express:

- S (average switching activity)

- C (average capacitance).

- Need of efficient methods for entropy calculation.

- Drawbacks: No delay modelling and no accounting of glitching effects.

Mod by Giorgio Fissore, pag 75

## Not Just Macromodelling

- Macromodelling is suited for datapath blocks.

- Ad-hoc models are required for other components:

- Memory

- Controllers

- Interconnect

SEBC-L4

MZ 46

## Memory models

- Parameters of the model belong to different categories:

- Structural: Rows, bit-width, bit per column, number of addressing lines.

- Timing: Time of the write-enable signal during write.

- Access-mode: Read, write, extra-read-before-write.

- Technology: Supply voltage.

- Dynamic: Address/data bus activity and number of toggles per access.

- *Non-componentized* (simpler) vs. *componentized* (more complex) models depending on target accuracy.

SEBC-L4

MZ 47

## Controller models

- Controller is a behavioral description (state machine).

- Accuracy loss is unavoidable.

- Approach: Account for complexity in the model:

$$P = F(\text{Activity}, \text{Complexity})$$

- Switching activity:

$$Esw(I) = \text{input switching activity}$$

$$Esw(O) = \text{output switching activity}$$

- Complexity:

$$Ni = \# \text{ of inputs}$$

$$Nc = \# \text{ of "cubes"}$$

$$No = \# \text{ of outputs}$$

Mod by Giorgio Fissore, pag 77

SEBC-L4

MZ 48

## Lecture 5

# Circuit Level Power Estimation

Appunti di Giorgio Fissore

Disponibili in centro stampa

- Domino CMOS Power Estimation

- Circuit-level methods

- ATPG methods

- Summary

SEBC-L5

MZ 1

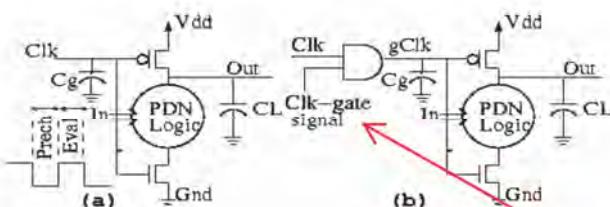

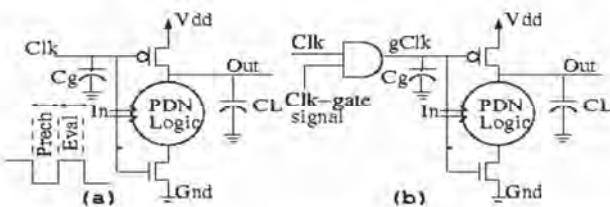

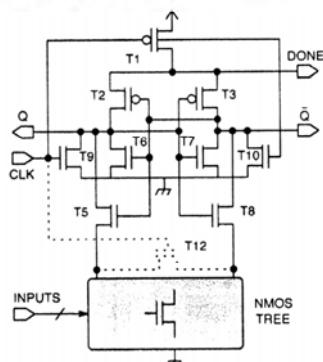

### Domino CMOS Power Estimation

- Unlike static CMOS, domino logic uses a precharging circuit and a 2-phase clocking regime

- During the precharging phase output is pulled-up while in the evaluation phase output possibly is discharged.

- Ignoring short-circuit and leakage currents, power must be calculated differently from static CMOS

SEBC-L5

MZ 2

### Domino CMOS Power Estimation

- Ignore direct-path short-circuit currents

- Average power over all circuit nodes:

$$\text{Power}_{\text{avg}} = \frac{1}{2} V_{dd}^2 \sum_i C_i A(i)$$

- $C_i$  = capacitive load of node  $i$ ,  $A(i)$  = activity of node  $i$

- Normalized power dissipation measure:

$$\Phi = \sum_i \text{fanout}_i \times a(i) \quad (3.64)$$

$\text{fanout}_i$  is # fanouts of node  $i$  (proportional to  $C_i$ ),

$a(i)$  = normalized activity =  $A(i)/T_{ck}$

Mod by Giorgio Fissore, pag 79

SEBC-L5

MZ 3

## Circuit Reliability

- Signal activity is a good measure of electro-migration and hot-electron degradation (happens only in saturation) in circuits

- Negative electro-migration leads to a *hillock*, or metal build-up, that can short adjacent metal lines

- Hot electron injection into gate oxide layer degrades  $g_m$  and  $V_t$ , cumulative over time, limits useful life of transistor

Il mio prodotto, una volta venduto, deve continuare a funzionare per un po'. Esistono dei fenomeni che invece ne accorciano la vita:

-Elettromigrazione: se la densità di corrente aumenta troppo, questa inizia ad erodere la pista nei punti più critici (come un fiume che, se troppo impetuoso, va a modificare il letto in cui scorre). Questo fenomeno inoltre, si autoalimenta con una reazione positiva: più una pista viene assottigliata, più, a parità di corrente, aumenterà la densità di corrente in quel punto, fino ad erodere completamente quella pista (trasformandola in un circuito aperto). **FENOMENO PERICOLOSO** perché al momento della produzione il circuito funziona, ma risulterà danneggiato magari dopo qualche mese.

-Hot-electron: elettroni ad alta energia, tendono ad alterare la struttura elettrica del dispositivo (vengono modificate transconduttanze, tensioni di soglia,...) fino a rendere il dispositivo non più funzionante.

SEBC-L5

MZ 7

## Circuit Reliability

- Mean time to failure (MTF) due to electro-migration:

$$MTF = \frac{K}{J^2} \quad (3.69)$$

- Minimize electro-migration by minimizing:

$$E = \sum_i C_i A_i \quad (3.70)$$

- $P_{avg} = I_{dd}V_{dd} = \frac{1}{2} (V_{dd}^{**2}) A_i C_i$

→ to minimize  $I_{dd}$  it is necessary to minimize  $A_i C_i$  !!!

- $J = \text{Average Current Density}$

- $K$  has statistical distribution, independent of  $J$

La densità di corrente, è legata al numero di commutazioni (qui chiamato  $A_i$ , ma è sempre la switching activity).

>> la corrente media è legata alla somma di tutte le  $E_{sw}$  moltiplicate per le capacità

>> noi ci occuperemo solo di ottimizzare la potenza, ma in questa maniera aumenteremo anche sempre la vita del dispositivo! (es se guido un'auto senza tirarla, ridurrò i consumi e ne allungherò la vita).

SEBC-L5

MZ 8

## Circuit Reliability (cont'd)

- As MOS scaled down, hot carriers are injected into gate oxide, due to lateral electrical field produced by source-drain voltage

- Trapping of these carriers degrades transistor transconductance and voltage threshold.

- More important, because oxide charging is cumulative over time → reduction of the life of the device

- $H_{gate} = A_{gate} f_{gate} = \text{hot electron degradation}$

$A = \text{gate activity}; f = \text{fanout}$

Mod by Giorgio Fissore, pag 81

SEBC-L5

MZ 9

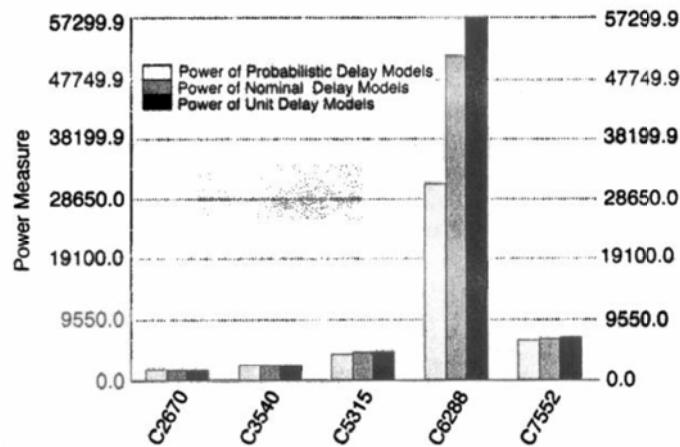

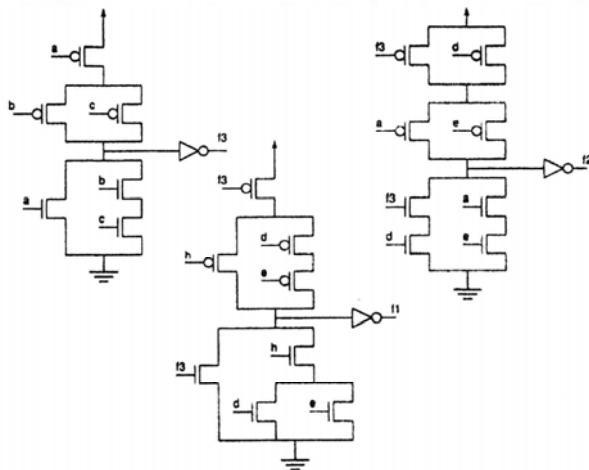

## Example: CMOS Gate

### Esempio 1

$x_1 = 0$

$x_2 = 0$

$x_3 = 1 \gg V_u = 1$

poi, cambia  $x_1$  creando un percorso per scaricare  $C_y$ .

In questo caso, visto che  $x_2$  sopra conduce ancora, si scaricherà anche  $C_{z1}$ .

### Esempio 2

Se invece al posto di  $x_1$  commutasse  $x_2$  (dal punto di vista logico ha lo stesso effetto), avrei una separazione tra il nodo  $z_1$  ed il nodo  $z_2 \gg C_{z1}$  questa volta non si scarica!!

SEBC-L5

MZ

QUINDI: gli ingressi, indistinguibili dal punto di vista logico, presentano ritardi e consumi diversi!! (diversa è la capacità da scaricare)  $\gg$  se ho segnali da far commutare velocemente, posso ottimizzarli collegandoli all'ingresso con il ritardo minore ( $x_2$ ). Questo causerà anche un minore consumo di potenza.

## Signal Connections to Minimize Power

- If  $x_2 = 0$ ,  $x_1 \rightarrow 1$  and  $x_3 = 1$  the capacitance to be discharged is  $C_y + C_{z1}$

- If  $x_1 = 0$ ,  $x_2 \rightarrow 1$ ,  $x_3 = 1$  only  $C_y$  is discharged during falling transition.

- It is important to connect external inputs to internal pins according to the activity!!!

- For instance if signal A has high activity and signal B has low activity, then connect A to  $x_2$  and B to  $x_1$  to minimize power

Regola generale: "più un transistor è vicino all'uscita, più va veloce e meno consuma" (meno nodi intermedi da caricare e scaricare)

SEBC-L5

MZ 14

"pin swapping": collegare ingressi con Esw maggiore, a quei pin che consumano meno!

## Signal Connections to Minimize Power

- Due to the internal nodes capacitance they need to be treated as circuit nodes distinct from outputs

- Activities of internal nodes must therefore be considered (np-hard!!!): unfortunately they depend on the previous clock cycles (as in sequential circuits)

- An accurate analysis of conducting paths from the nodes and Vdd and Gnd is required.

Mod by Giorgio Fissore, pag 83

SEBC-L5

MZ 15

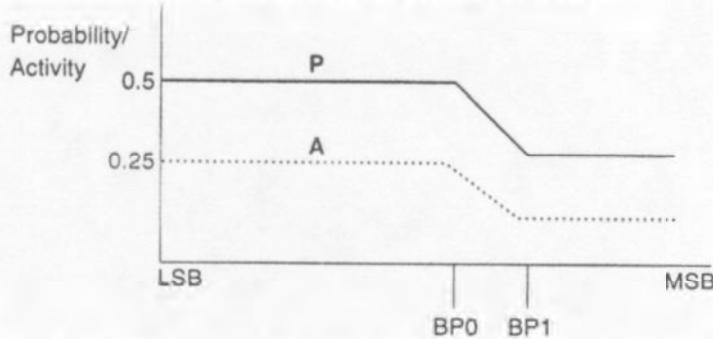

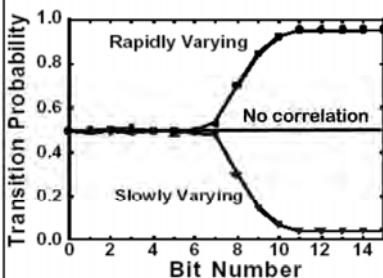

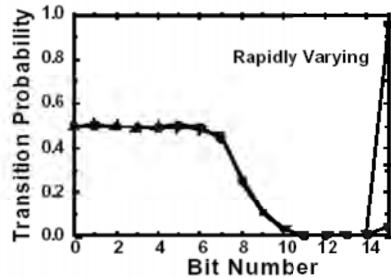

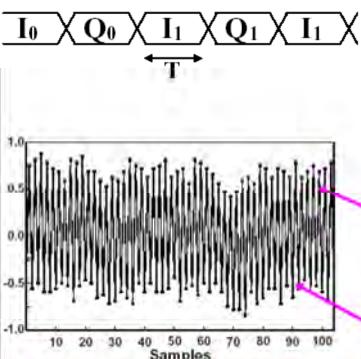

## Word-Level Data Model

- Signal prob. of lower order bits of a word are uncorrelated in space and time (independent of data distribution)

- BP0 and BP1 are breakpoints tied to statistical parameters and define when correlation starts

## Most Significant Bit Data Models

- $F_1$  = bivariate normal distribution function

- $F_{01}$  = univariate normal distribution function

- $\rho_1$  = lag 1 correlation coefficient

- Breakpoint equations (where MSB correlation starts):

$$BP_0 = \log_2 \left( \frac{3\sigma}{32} \right)$$

$$BP_0 = \log_2 \left( \frac{3\sigma}{32} \right) - \log_2 (1 - \rho_1^2)^{0.5}$$

$$P_{MSBs} = F_1 \left( \frac{\mu}{\sigma} \right)$$

$$A_{MSBs} = F_{01} \left( \frac{\mu}{\sigma}, \rho_1 \right)$$

$$BP_1 = \log_2 (|\mu| + 3\sigma)$$

## Information Theoretic Approaches

- Estimate power at Register Transfer Level

- Estimate entropy and use it to find signal activity

- Entropy  $H(x)$  defined in terms of signal probability  $p$ :

$$H(x) = p \log_2 \frac{1}{p} + (1 - p) \log_2 \frac{1}{1 - p}$$

- For discrete-valued signal  $x$ , with  $n$  values:

$$H(x) = \sum_{i=1}^n p_i \log_2 \frac{1}{p_i}$$

Mod by Giorgio Fissore, pag 85

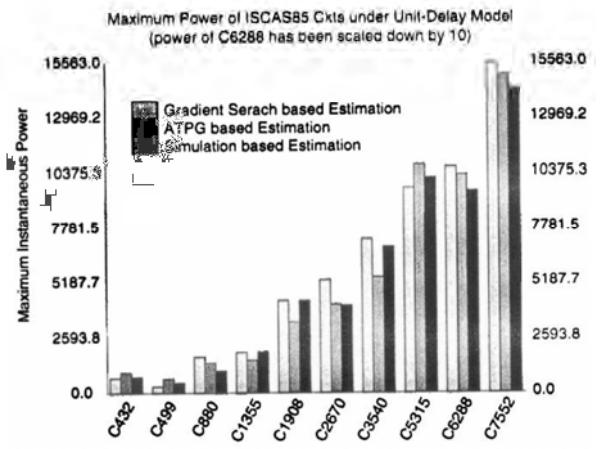

## ATPG vs. Gradient vs. Simulation Methods – Unit Delay Model

SEBC-L5

MZ 25

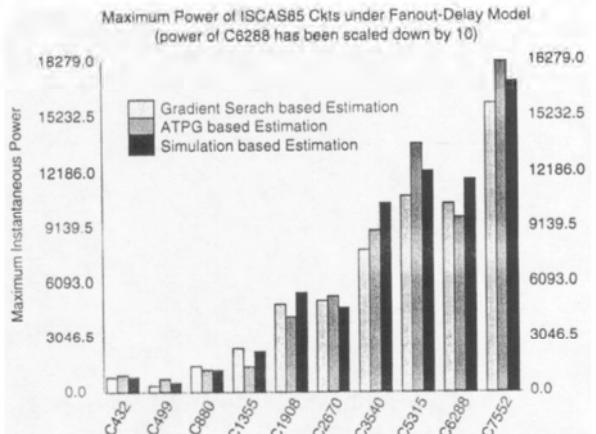

## ATPG vs. Gradient vs. Simulation Methods – Fanout Delay Model

SEBC-L5

MZ 26

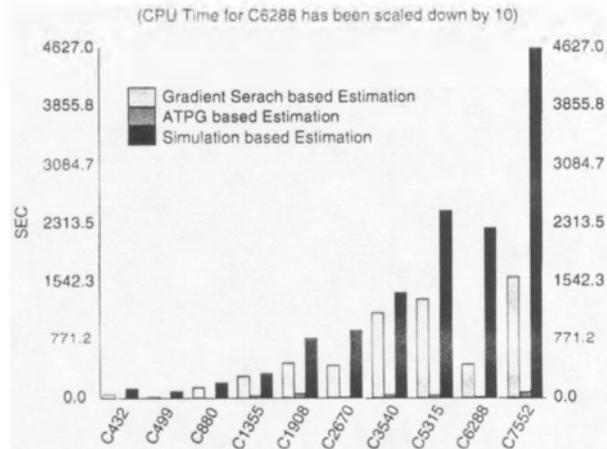

## CPU Time Comparisons for Unit Delay Model Circuits

SEBC-L5

MZ 27

Mod by Giorgio Fissore, pag 87

## Summary of Power Estimation

- Circuit-level and High-level power estimators exist

- Maximum power estimated with ATPG tools, using steepest-descent gradient descent, or genetic algorithms

Esempi di quanto posso ottimizzare sui vari livelli

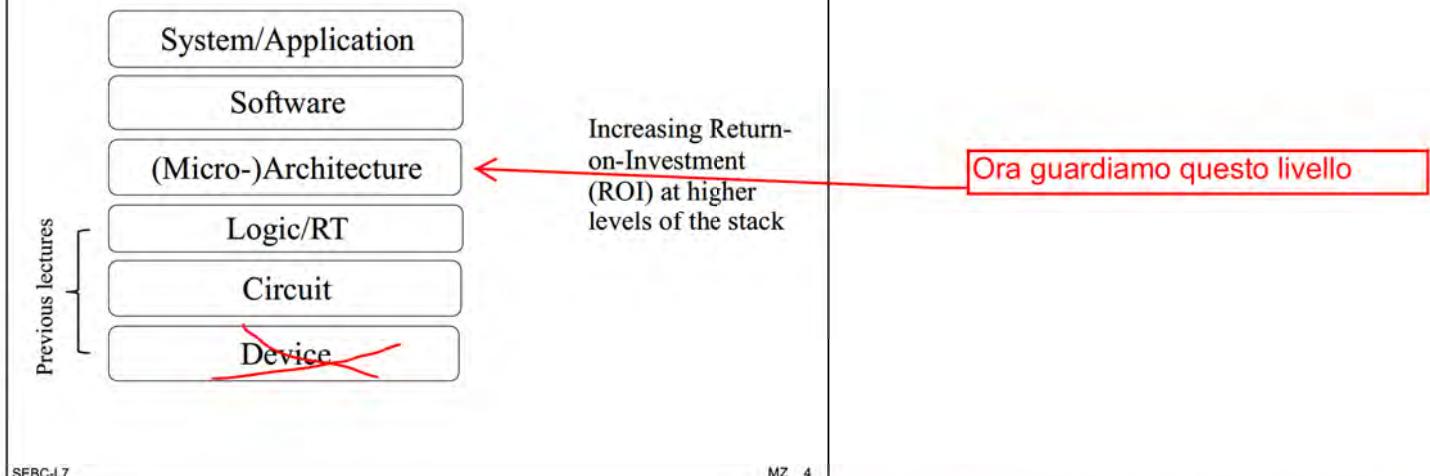

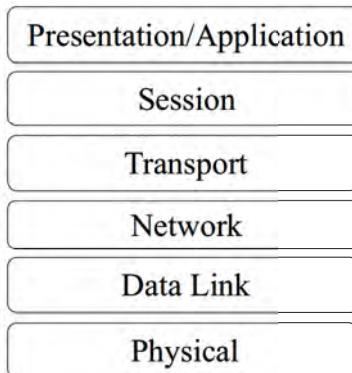

## The Design Abstraction Stack

A very rich set of design parameters to consider!

It helps to consider options in relation to their abstraction layer

70%

30%

3%

3%

|                      |                                                                        |

|----------------------|------------------------------------------------------------------------|

| System/Application   | Choice of algorithm                                                    |

| Software             | Amount of concurrency                                                  |

| (Micro-)Architecture | Parallel versus pipelined, general purpose versus application specific |

| Logic/RT             | logic family, standard cell versus custom                              |

| Circuit              | sizing, supply, thresholds                                             |

| Device               | Bulk versus SOI (silicon on insulator)                                 |

Posso cercare di ottimizzare il mio progetto su livelli differenti.

Tendenzialmente, più vado verso l'alto, più ho risparmi significativi.

Anche l'algoritmo può essere modificato per ottimizzare i consumi (così come per le prestazioni).

Es. "probabilmente l'algoritmo che muove meno dati è quello che consuma di meno"

Noi non ci occuperemo solo di questo livello (si vedrà in altri corsi)

## Optimization Can/Must Span Multiple Levels

Design optimization combines top-down and bottom-up:

"meet-in-the-middle"

Mod by Giorgio Fissore, pag 91

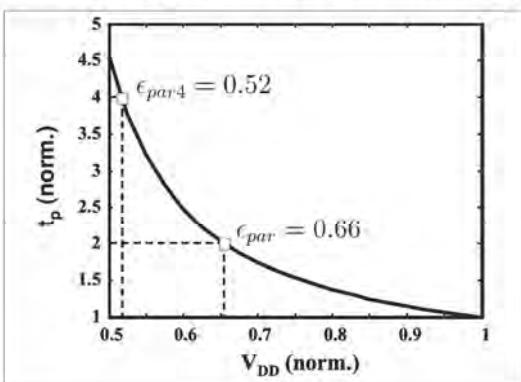

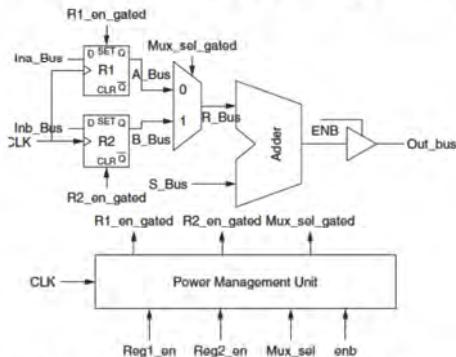

## Reducing Active Energy @ Design Time

$$E_{active} \sim \alpha \cdot C_L \cdot V_{swing} \cdot V_{DD}$$

$$P_{active} \sim \alpha \cdot C_L \cdot V_{swing} \cdot V_{DD} \cdot f$$

### ◆ Reducing voltages

- ◆ Lowering the supply voltage ( $V_{DD}$ ) at the expense of clock speed

- ◆ Lowering the logic swing ( $V_{swing}$ )

### ◆ Reducing transistor sizes ( $C_L$ )

- ◆ Slows down logic

### ◆ Reducing activity ( $\alpha$ )

- ◆ Reducing switching activity through transformations

- ◆ Reducing glitching by balancing logic

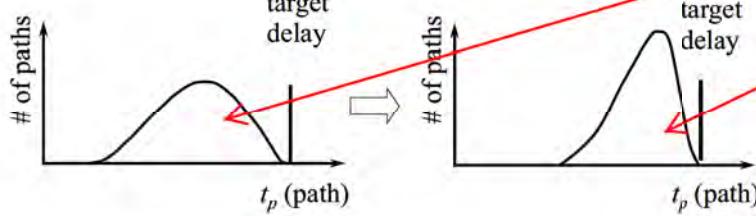

## Observation

- ◆ Downsizing and/or lowering the supply on the critical path lowers the operating frequency

- ◆ Downsizing non-critical paths reduces energy for free, but

- ◆ Narrows down the path delay distribution

- ◆ Increases impact of variations, impacts robustness

Prima del corso di low power avevo percorsi più lenti e percorsi più veloci distribuiti abbastanza uniformemente; la cosa importante era non superare un target delay

Ora invece cerchiamo di accumulare tutti i ritardi verso il limite; in questo modo, pur mantenendo lo stesso ritardo, ottimizzo la potenza (pensare alla curva potenza-ritardo)

Attenzione che spostare i ritardi sempre più vicino al target delay impatta anche la robustezza del circuito, poiché se un ritardo aumenta per qualche motivo, è ora più probabile che questo superi la soglia causando un malfunzionamento.

## Circuit Optimization Framework

$$\begin{array}{ll} \text{minimize} & \text{Energy } (V_{DD}, V_{TH}, W) \\ \text{subject to} & \text{Delay } (V_{DD}, V_{TH}, W) \leq D_{con} \end{array}$$

### Constraints

$$\begin{aligned} V_{DD}^{\min} < V_{DD} < V_{DD}^{\max} \\ V_{TH}^{\min} < V_{TH} < V_{TH}^{\max} \\ W^{\min} < W \end{aligned}$$

### ▪ Reference case

- $D_{min}$  sizing @  $V_{DD}^{\max}$ ,  $V_{TH}^{\text{ref}}$

Mod by Giorgio Fissore, pag 93

## Library Gate Delay Model

- For every input terminal  $I_i$  and output terminal  $O_j$  of every gate:

- $T_{i,j}^i(G)$  – fanout load independent delay (intrinsic)

- $R_{i,j}(G)$  – additional delay per unit fanout load

- Total gate propagation delay from input to output:

$$T'_{i,j}(G) = T_{i,j}^i(G) + R_{i,j}(G)C_j(G)$$

- Normalize all activities  $d_y$  by dividing them by clock activity ( $2f$ ) -  $f$  is the clock frequency -

- Probability of rising or falling transition at  $y$ :

$$p_y^{\uparrow} = d_y \quad (4.27)$$

$$p_y^{\downarrow} = p_y^{\uparrow} = \frac{1}{2}p_y^{\uparrow} \quad (4.28)$$

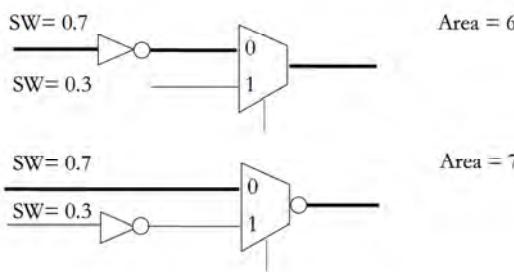

## Technology Mapping for Low Power

- Problem statement:

- Given Boolean network optimized in a technology-independent way and a target library, bind network nodes to library gates to optimize a given cost

- Method:

- Decompose circuit into trees

- Use dynamic programming to cover trees

- Cost function:

$$\text{Area}(g) + \sum_{n_i \in \text{inputs } (g)} \text{MinArea}(n_i) \quad (4.23)$$

- Traverse tree once from leaves to root

## Extension for Low-Power Design

- Power dissipation estimate:

$$\text{Power} = \sum_{i=1}^{j=n} \frac{1}{2} V_{dd}^2 a_i C_i f \quad (4.24)$$

- Estimate partial power consumption of intermediate solutions

- Cost function:

$$\text{power}(g, n) = \text{power}(g) + \sum_{n_i \in \text{inputs } (g)} \text{MinPower}(n_i) \quad (4.25)$$

- $\text{power}(g, n)$  = cost of choosing gate  $g$  to match at node  $n$

- $\text{MinPower}(n_i)$  is minimum power cost for input pin  $n_i$  of  $g$

- $\text{power}(g) = 0.5 f V_{DD}^2 a_i C_i$

- Formulation:

$$\text{Minimize } wP + (1-w)R \text{ such that } T \leq T_{max}$$

- $R$  = Total Area,  $w$  gives their relative importance;  $T$  = delay

Mod by Giorgio Fissore, pag 95

## Calculating Transition Probability

- Hard to find  $p_{zi}^{\uparrow}$  (NP-hard)

- Hard to determine prior state of internal circuit nodes

- Assume that when state cannot be determined, a transition occurred (upper power limit)

- More accurate bound: Observe that # conducting paths from node to  $V_{dd}$  must change from 0 to > 0 followed by similar change in # conducting paths to  $V_{ss}$

- Use # conducting paths that is smaller

- $$p_{zi}^{\uparrow} = \begin{cases} p_{zi,V_{dd}}^{\uparrow} & \text{if } p_{zi,V_{dd}}^{\uparrow} \leq p_{zi,V_{ss}}^{\uparrow}, \\ p_{zi,V_{ss}}^{\uparrow} & \text{otherwise} \end{cases}$$

- Use serial-parallel graph edge reduction techniques

SEBC-L6

MZ 22

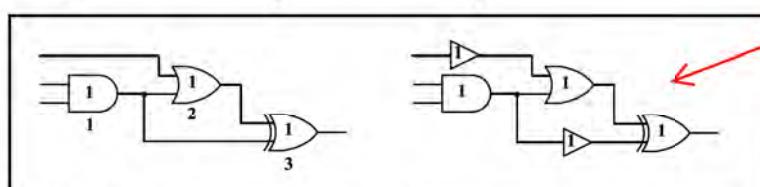

## Transistor Reordering

- Already know delay of longest paths through each gate input from static timing analyzer

- Should (for NAND or NOR) connect latest arriving signal to input with smallest delay

- Break gate inputs into permutable sets and swap inputs

- Hard to compute which input order is best – can afford to enumerate all possible orderings and try them

- Compute prob. (signal is switching while all other signals in permutable set are on) – gives maximum internal node C charging / discharging

SEBC-L6

MZ 23

## Transistor Reordering: Pin Swapping

- Library gates generally have pins that are functionally equivalent.

- Permutations of these pins are possible.

- Internal capacitance ignored: assign high switching nodes to low input capacitance pins.

- Internal capacitance considered: must consider all possible permutations of assignments.

- Explicit enumeration is feasible (inputs in a cell typically less than 6-8)

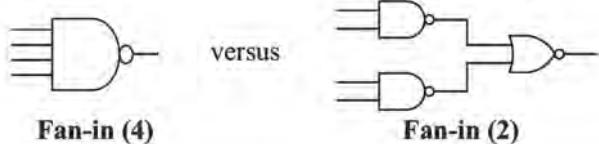

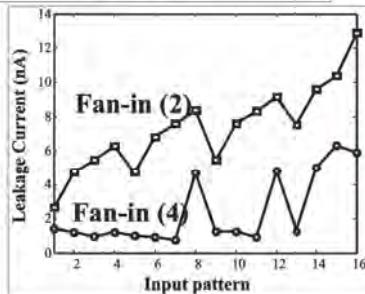

Rispetto a prima stanno aumentando i vantaggi di porte a più ingressi. Ora non sempre la cascata di porte è migliore rispetto alla singola porta a tanti ingressi.

Questo complica il pin swapping, poiché vengono usate sempre più spesso queste porte, ma lo rende sempre più importante, dato che gli ingressi sono equivalenti dal punto di vista logico, ma cambiano se si guardano i ritardi.

Queste modifiche fanno parte del livello di SCELTA DELLA TECNOLOGIA!

Mou by Giorgio Tissore, pag 77

SEBC-L6

MZ 24

## Transistor Resizing Methods

- Typical cell libraries have several instances of cells with different sizes.

- Replace some gates of the circuit with library gates having smaller area, but smaller capacitive load. Smaller gates are also slower....

- Idea:

- Replace only gates not belonging to critical paths.

- Can be used to further improve the result of power-targeted technology mapping.

Questo metodo può portare a miglioramenti di prestazioni di qualche per cento.

SEBC-L6

MZ 28

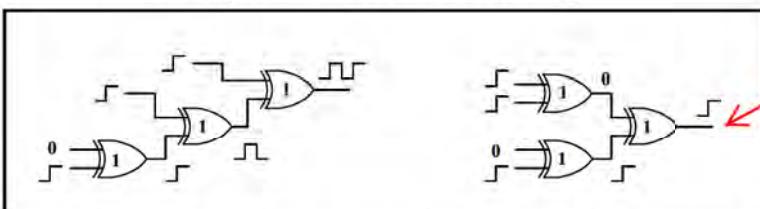

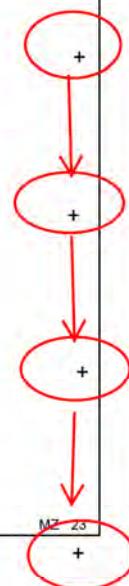

## Technology mapping

Larger gates reduce capacitance, but are slower

Come vado a lavorare?

individuo il percorso critico e vado a lavorare sugli altri percorsi, tendendo a portare anche loro sul limite di ritardo.

(nel caso a fianco posso ridurre le dimensioni delle porte cerchiate).

Questo processo fa parte del TECHNOLOGY MAPPING, la scelta della tecnologia.

SEBC-L6

MZ 29

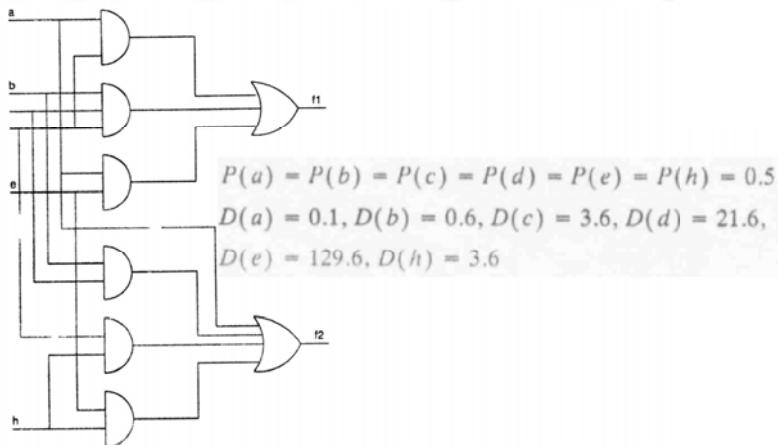

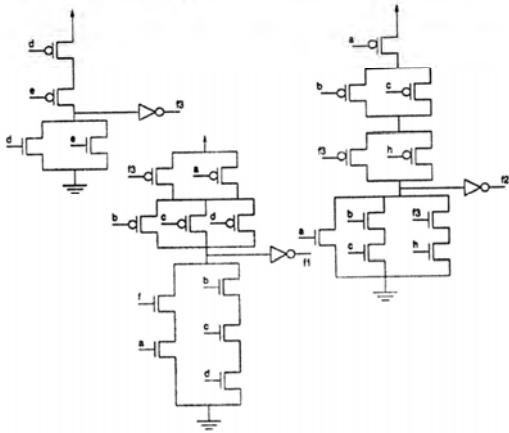

## Technology Mapping: 4 input AND

### Example: 4-input AND

- (a) Implemented using 4 input NAND + INV

- (b) Implemented using 2 input NAND + 2-input NOR

Library 1: High-Speed

Library 2: Low-Power

| Gate type | Area (cell unit) | Input cap. (fF) | Average delay (ps) | Average delay (ps) |

|-----------|------------------|-----------------|--------------------|--------------------|

| INV       | 3                | 1.8             | $10.7 + 5.4 C_L$   | $12.0 + 6.0 C_L$   |

| NAND2     | 4                | 2.0             | $10.3 + 5.3 C_L$   | $16.3 + 8.8 C_L$   |

| NAND4     | 5                | 2.0             | $13.6 + 5.8 C_L$   | $22.7 + 10.2 C_L$  |

| NOR2      | 3                | 2.2             | $7.0 + 3.8 C_L$    | $16.7 + 8.9 C_L$   |

La logica CMOS è per natura invertente.

Come realizzare una NAND a quattro ingressi?

SEBC-L6

MZ 30

Mod by Giorgio Fissore, pag 99

NAND e NOR a due ingressi

hanno dimensioni diverse!!

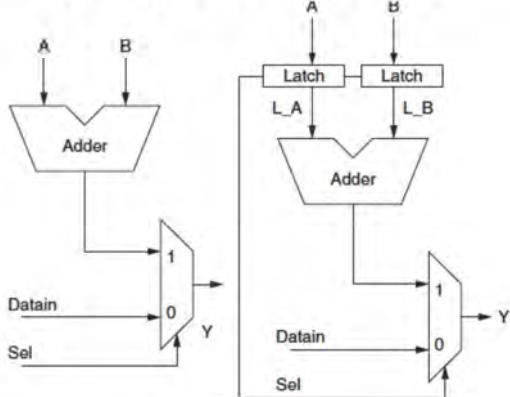

## Buffer Insertion

- Selective insertion of buffers to reduce capacitance and transition times.

- Requires accurate timing information (i.e. fully mapped netlist).

- Example: for a NAND gate driving two FFs a buffer can be inserted to speed up the signal transition times.

- Internal power without buffer:

NAND = 3 ; FF 5 x 2  $\rightarrow$  Transition time = 4

- Internal power with buffer:

NAND = 2,5 ; Buffer = 1; FF=4,5 x 2  $\rightarrow$  Transition time = 2

Esempio: immaginiamo di avere una NAND che deve pilotare due FFs.

La NAND (ottimizzata per un carico) ha un suo consumo (es 2.5 per un gate, 3 per due gate), ogni FF consuma 5  $\gg$  tot =  $5*2+3=13$ , e transizioni lente

Risintesi: aggiungo un buffer (che consuma 1).

ora la NAND pilota solo più un carico, e il buffer è in grado di dare fronti più ripidi; grazie a questi il circuito va più veloce, e i FFs consumano meno, poiché viene ridotta la loro corrente di corto.

SEBC-L6

MZ 34

## Phase Assignment

- Selectively reduce transitions on high-activity nets by assigning the most proper polarity.

- Trade off possible area increase for power

Esempio 2:

Guardando il caso a lato, se nella mia libreria ho anche un mux invertente (con consumi simili a quello non invertente), allora se sposto l'inverter sul secondo ingresso, ne più che dimezzo i consumi! (grazie alla minore Esw)

SEBC-L6

MZ 35

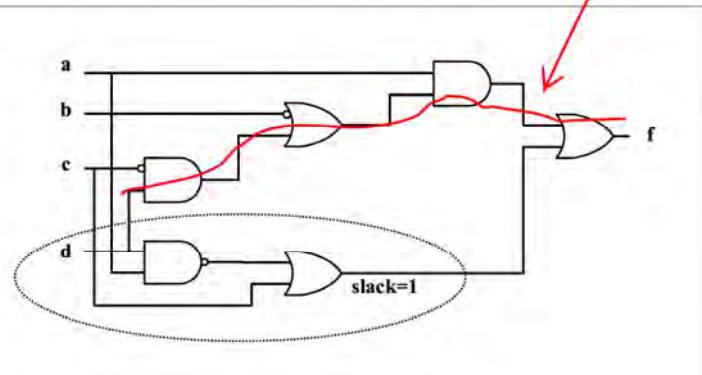

## Logic Restructuring

Logic restructuring to minimize spurious transitions

Altri esempi:

La soluzione ad albero è sempre meno sensibile ai glitch

Buffer insertion for path balancing

Inserisco un buffer per rendere più bilanciati i percorsi (dal pt di vista dei ritardi)

Mod by Giorgio Fissore, pag 101

SEBC-L6

MZ 36

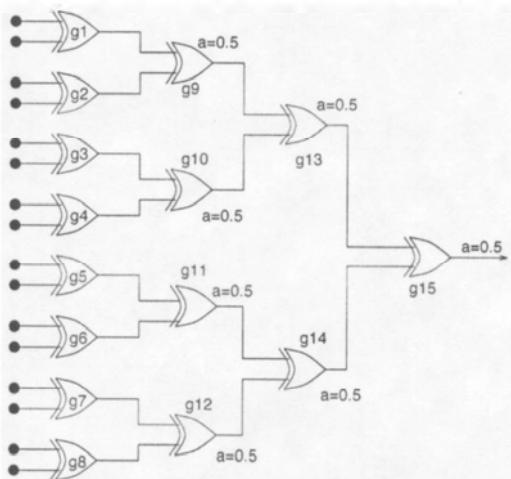

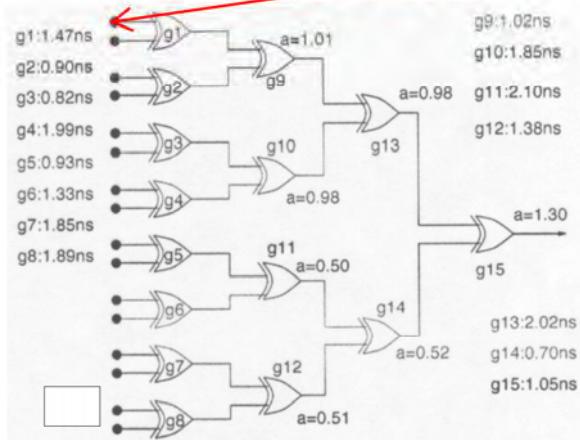

## Impact of Signal probabilities

$$Esw(a) = p1(1-p1) + p4(1-p4) + p5(1-p5) + p13(1-p13) + p7(1-p7)$$

$$Esw(b) = Esw(a) - 2p1p5$$

$$Esw(c) = Esw(a) - 2p5p13$$

$$Esw(d) = Esw(a) - 2p1p5 - 2p4p5 - 2p5p7 - 2p5p13 + 3p5(1-p5)$$

$$Cost(a)=20$$

$$Cost(b)=15$$

$$Cost(c)=15$$

$$Cost(d)=12$$

SEBC-L6

MZ 40

## Impact of Signal probabilities

- Esw(b) and Esw(c) are obtained by merging cubes into larger ones.

- Esw(b), Esw(c) < or = Esw(a) regardless of signal probabilities.

- Does finding larger cubes result in less activity? **In general, it does not!!!**

- The value of Esw(d) w.r.t. Esw(a) depends on signal prob.

- Example: If the input signals have all 0.5 probabilities, Esw(d) is higher than any of Esw(a), Esw(b) and Esw(c).

SEBC-L6

MZ 41

## Impact of Signal probabilities

- The cost function must be a function of signal probabilities.

- Merging cubes into larger cubes reduces switching.

- Example: Covering vertex i and j to form a cube reduces Esw of  $2p_i p_j$ .

- Covering a vertex more than once increases switching.

- Example: Covering vertex with n cubes increases Esw of  $(n-1)p_i(1-p_i)$

- Rules of thumb:

- The larger the number of vertices that a merged cube can cover, the larger the power reduction.

- Usually, covering a vertex more than once causes unnecessary power dissipation.

SEBC-L6

MZ 42

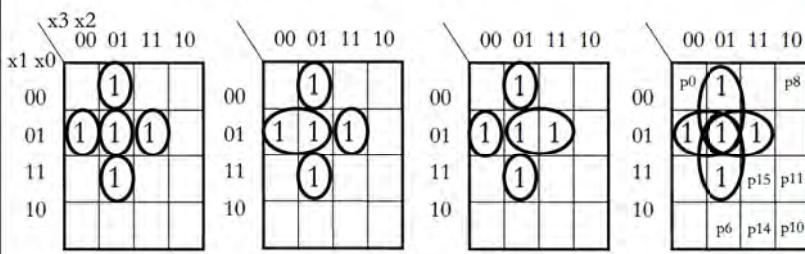

a) posso coprire i 5 uni con 5 implicanti con una somma di 5 termini>>avrei 5 AND a 4 ingressi che vanno dentro ad una OR. (se coprissi gli zeri, or in ingresso, and in uscita) La formula Esw(a) riguarda proprio le 5 AND (si dovrebbe poi ancora aggiungere la Esw dell'uscita).

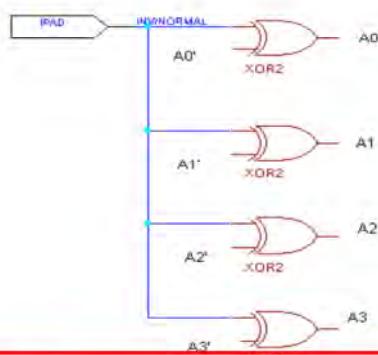

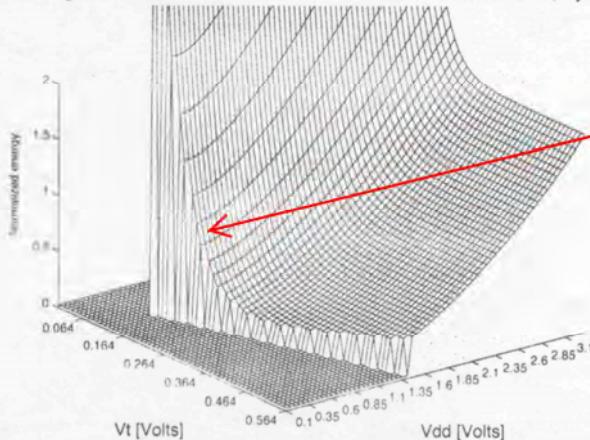

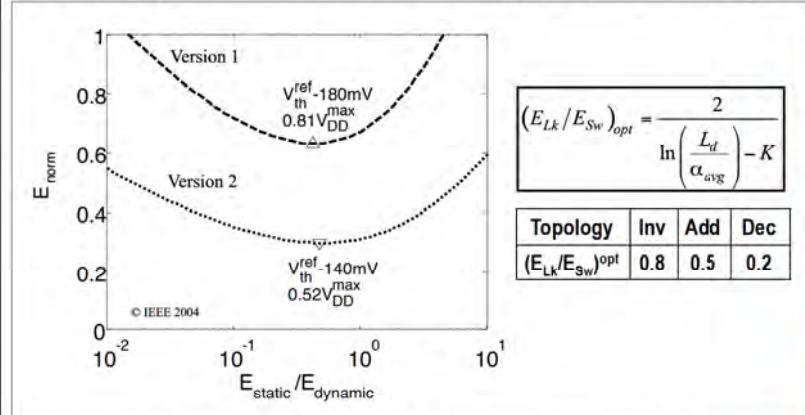

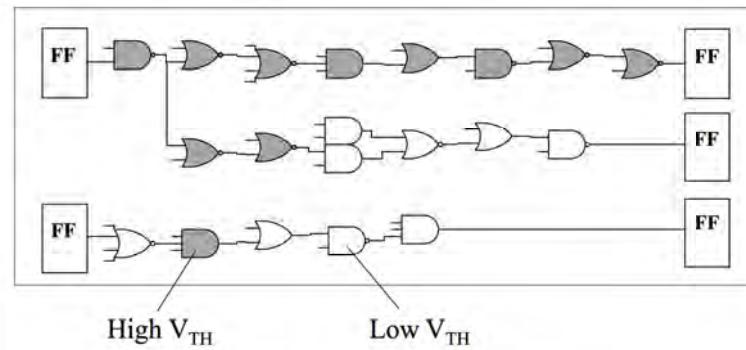

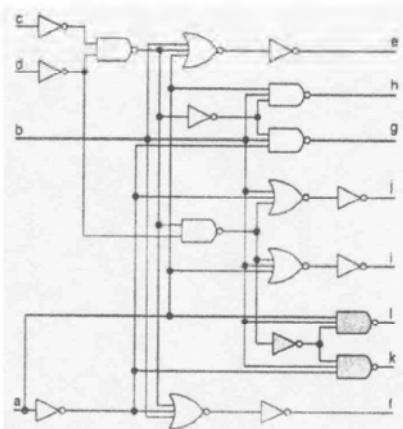

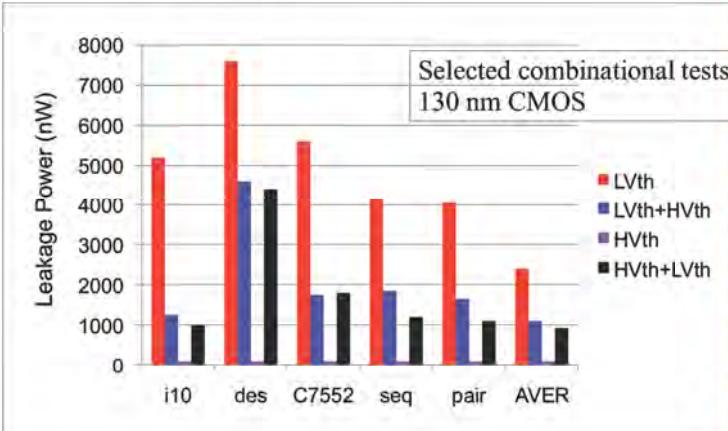

[il modo più semplice per etichettare gli implicanti è chiamarli con il numero ottenuto concatenando le coordinate, es 01-00 >> 4]